Abstract — – This paper provides the design of keystream generators utilizing low hardware and low power based circuits, so called LFSR ( Linear Feedback Shift Register ) circuits. It includes the design of 2 watercourse cyphers based on hash maps and a category of binary keystream generator called modified clock-controlled jumping measure generator ( a„¦k ) . The parametric quantities like cyclicity, attacktime and throughput of watercourse cyphers are calculated. The irregular clocking in a„¦k provides good security against assorted cryptanalytic onslaughts. Analysis is made for the coevals of keystream for clock controlled generator.

FPGA consequences of watercourse cyphers and CCG evaluate their hardware efficiencies. As per the consequences, the first watercourse cypher gives high cyclicity, low attacktime and high throughput. The 2nd watercourse cypher gives low cyclicity, high attacktime and low cyclicity compared to first one. Whereas, the 3rd one provides good cyclicity, high attacktime and good sum of security. In all the three designs, keystream coevals plays a major function.

Keywords-Linear Feedback Shift Register, Stream Cipher, Alternating Step Generator, clock controlled generator, Filter generator, Keystream generator, Modular division circuit.

Secret key cyphers are classified into 2 types, block cyphers and watercourse cyphers. Block cyphers are the clip changing transmutation of group of informations spots and watercourse cyphers are the clip changing transmutation of single or watercourse of informations spots. It includes internal memory in watercourse cyphers whereas in block cyphers, no internal memory is involved. Stream cyphers are of import category of encoding algorithms because of their low hardware complexness and power ingestion.

They encrypt binary figures of plaintext message at a clip, utilizing an encoding transmutation that varies with clip. They are

fast and more appropriate and in some instances compulsory ( illustration in some communications applications ) , when buffering is limited or when characters are separately processed during response. Because of their low mistake extension standards, watercourse cyphers are advantageous in state of affairss where transmittal mistakes are extremely likely.

A binary linear watercourse cypher is merely an XOR operation of field text and keystream spots. It consists of keystream, plaintext and cypher text in the signifier of binary sequences. Each secret key K is given as an input to the keystream generator that generates a keystream sequence. Since the secret key K is shared between the sender and receiving system, the receiving system can decode by XOR’ing the end product of the keystream generator with the cypher text, obtaining the message sequence. Keystream coevals plays a major function in the security of the system. Hash maps are normally used in communicating devices, particularly for unity confirmation and hallmark of informations and control packages. Basically a hash map is a map that maps a message of variable length to a fixed length hash value that serves as an appraiser. Hence a watercourse cypher based on hash map is a really good option in cut downing hardware complexness of the cryptosystem. So a hash based watercourse cypher with low hardware complexness is of import in the design of many cryptosystems. Based on the use of hash map the security of PRNG varies.

A cryptographically strong Pseudo Random Number Generator ( PRNG ) is the bosom of any watercourse cypher. A pseudo random figure generator is a deterministic multinomial clip based algorithm, which expands short seeds into longer spot sequences. Two methods of bring forthing cryptographically strong PRNG are LFSR strategies and Oneway map based strategies. Linear Feedback Shift Registers are the most normally used watercourse cyphers due to the low hardware complexness and less power ingestion. The chief drawback of LFSR based watercourse cyphers is susceptibleness to assail due to the one-dimensionality in the construction. Two major strategies to destruct the built-in one-dimensionality in LFSRs are taking end product through non-linear Boolean map and irregularly timing LFSRs ( clock controlled generator ) . Boolean map can be used to unite the end products of several LFSRs or end products of different memory elements of a individual LFSR giving rise to nonlinear combination generator and filter generator structures severally. Step1-step2 generators, jumping measure generators, shriveling and self-shrinking generators belong to the class of the clock controlled generators ( CCG ) where the LFSR bring forthing the keystream is clocked at different intervals. The lone drawback of irregular clocking is keystream period gets shortened, but as per the security it gives best consequences.

A category of spot orientated cardinal watercourse generator a„¦k is proposed in this paper and is related to category of the ASG ( Alternating Step Generator ) . ASG belongs to the household of CCG category. Here, the keystreams generated by K generator Gk are of long period, high complexness and nice statistical distribution belongingss. It uses three feedback displacement registry R1, R2 and R3 in the coevals of keystream. The first registry R1 alterations province as a usual FSR ( Feedback Shift Register ) where as the other 2 registries R2 and R3are clocked utilizing a clocking mechanism. After the clocking, the end product spot is produced at the end product of Gk. Keystreams generated by a Gk are obtained by XOR’ing end products of all 3 shift-registers R1, R2 and R3. Correlation onslaught is one of the powerful onslaughts on watercourse cyphers based on FSRs and is considered as one of the most serious menace against the security of watercourse cyphers. If a cryptographer manages to observe a correlativity between the known keystream section and the end product of one LFSR ( when on a regular basis clocked ) , this can be utilized in a divide and conquer onslaught on this LFSR. So, proper keystream coevals improves the security.

This chapter deals with the proposals of 3 watercourse cyphers and the hardware analysis, cyclicity and onslaught clip of both the watercourse cyphers.

STREAM CIPHER1: Stream cypher 1 is a combination of LFSR based toeplitz hash coevals circuit and LFSR based keystream generator circuit.

Let a message M consists of length ‘m ‘ spots and the end product hash be of ‘n ‘ spots. In order to bring forth a matrix of order n*m, we need nm elements. By utilizing Toeplitz matrix construction it is possible to accomplish the matrix of order m*n by utilizing m+n-1 spots. The Toeplitz matrix is characterized by the belongings that each column in the matrix is obtained by switching down the old column and adding a new component to the top of the column. Let the initial province of LFSR hash be ( s0, s1, s2, s3, s4 ) = ( 0 0 0 1 0 ) and the LFSR hash multinomial be h ( ten ) = x5 + x2 + 1. Since the grade of H ( x ) is 5, n = 5 and the figure of message spots be m=9. Harmonizing to Toeplitz standards, it needs merely m+n-1 spots, ( here, 9+5-1=13 spots ) in order to bring forth a matrix. So utilizing the above mentioned feedback multinomial and initial province, the 13 spot end product sequence of the LFSR is ( s0, s1, . , s12 ) = ( 0 0 0 1 0 1 0 1 1 1 0 1 1 ) . The Toeplitz matrix is formed by composing the initial sate of the LFSR get downing from the underside as the first column of the matrix. The back-to-back columns are obtained by switching down the old column by one spot and adding the new spot obtained after each clock to the top of the column. LFSR o/p sequence = [ 0 0 0 1 0 1 0 1 1 1 0 1 1 ]

Toeplitz matrix ( 5 x 9 ) =

0 1 0 1 1 1 0 1 1

1 0 1 0 1 1 1 0 1

0 1 0 1 0 1 1 1 0

0 0 1 0 1 0 1 1 1

0 0 0 1 0 1 0 1 1

Let the 9 spot message be [ 0 0 0 0 1 0 0 0 1 ] .

Then the hash value is obtained by change by reversaling the spots obtained by multiplying the Toeplitz matrix with the column matrix of the message. Hash value produced is [ 1 0 0 0 0 ] .

0 1 0 1 1 1 0 1 1

1 0 1 0 1 1 1 0 1

0 1 0 1 0 1 1 1 0 * ( 0 0 0 0 1 0 0 0 1 ) ^T

0 0 1 0 1 0 1 1 1

0 0 0 1 0 1 0 1 1

= ( 1 0 0 0 0 ) ^T

The conventional diagram of LFSR based Toeplitz matrix is shown below. In the figure, the control registry and switch registry together forms the LFSR, whereas, the control registry defines the feedback multinomial of the LFSR. The LFSR changes its province with each message spot. If the message spot is ‘1 ‘ , the corresponding province is accumulated into an accretion registry and if it is ‘0 ‘ the province is non accumulated.

Figure.1 Schematic diagram of LFSR based Toeplitz matrix

See a message of length ‘m ‘ spots and end product ‘n ‘ spots. Let ‘KEY ‘ be the initial random seed, ‘h ‘ be the hash map and Eleven be the hash map end product after ith loop and S1, S2, S3, .. be the sequence of strings generated by a deterministic map ‘F ‘ . The first phase end product is X1=h ( KEY||S1 ) , i.e. , concatenation of KEY and initial twine. To acquire the following twine in the sequence of keystream, hash a modified version of the old end product twine is concatenated with the new random spots generated by the deterministic map ‘F ‘ . The mathematical theoretical account of proposed watercourse cypher is represented as below.

X1=h ( KEY || S1 )

X2=h ( ( KEYX1 ) ||S2 )

X3=h ( ( KEYX2 ) ||S3 )

Xn=h ( ( KEYXn-1 ) ||Sn )

Keystream=X1 ||X2 ||X3 ||aˆ¦aˆ¦..||Xn ;

Figure.2 PRNG cardinal watercourse generator

Stream cypher 1 is a combination of LFSR based toepliz hash coevals circuit and LFSR based keystream generator circuit. The construction of lfsr based toeplitz hash is shown below. Algorithm stairss: 1 ) whenever the input is high, the provinces of LFSR are loaded into the registry. 2 ) If the input is low, the provinces are discarded. 3 ) Once once more if the input is high, 5 spot registry is XORed with current contents in flipflops of LFSR and old end product of registry is modified by present XOR end product. 5 spot registry is clocked merely when message is high.

Figure.3 LFSR based toeplitz hash

Hardware Implementation: A0 to A4 represents the province of the LFSRT and is initialized. The feedback multinomial of the LFSRT block used in the construction is taken as H ( x ) =x5+x2+ 1. Since the grade of the LFSRT multinomial of the hash block is 5, figure of spots in the hash end product is n= 5. Therefore m-n=4, i.e. , the grade of feedback multinomial of threading bring forthing LFSRS is taken as 4. The figure of spots in the input of hash map block ‘m=9 ‘ . The chief blocks in the realisation of the LFSR based Toeplitz hash map are LFSRT and collector. Therefore 9 spots input are serially fed to the hash map block. The LFSRT advances its province with each of the input spots. If the input spot is 1, the corresponding province ( A0 to A4 ) of the LFSR is stored in a 5 spot registry. If the input spot is 0, so the corresponding province is discarded. The following clip when the input spot is 1 the provinces of the 5 spot registry is XORed with the current contents of the flipflops of the LFSR and the old end product of the registry is modified by the present XOR end product and is stored as a new end product ( Y0 to Y4 ) . The 5 spot registry is clocked merely when the message spot is high. The concluding content of the registry after all the inputs are fed to the hash map block is the concluding hash value. The keystream spots of the proposed theoretical account are the consecutive end product from the hash map block.

Consequences: The platform used is MATLAB ( for ciphering cyclicity and onslaught clip ) and XILINX ISE 10.1, FPGA ( for hardware design ) . The cyclicity of the theoretical account can be defined as n ( 2n-1 ) ( 2 ( m-n ) -1 ) ) , where ‘m ‘ is the length of input to the hash map in footings of figure of spots and ‘n ‘ is the grade of multinomial. The throughput is defined as the ratio of the figure of end product random spots to the figure of input random spots and is given by [ Ns ( 2n-1 ) ( 2 ( m-n ) -1 ) ) ] /m, which can be much larger than that of a simple LFSR based watercourse cypher given as ( 2m- 1 ) /m for a proper choice of ‘m ‘ and ‘n ‘ . For illustration with n=4, m=8, throughput for LFSR based watercourse cypher is 31.89 while that for the proposed theoretical account is 112.5. Time period for LFSR is 255 and for the proposed theoretical account is 900. Time period of the cardinal stream= N ( 2n-1 ) ( 2 ( m-n ) -1 ) ) and attack clip = O ( 2k ) .

Hash o/p length N ( spots )

Hash i/p length m ( spots )

Time period of cardinal watercourse

Attack-time

4

7

422

0.09s

5

8

1025

0.17s

5

9

2325

0.81s

7

11

13335

4.81s

7

13

157,619

206.9s

11

15

337,755

1653.3s

Table1 shows the cyclicity and attacktime consequences for assorted m, n values

From the above tabular array it is observed that the cyclicity increases at a high rate and for high values of m, n the attacktime besides increases quickly. The simulation consequences of LFSR based Toeplitz hash is shown below.

Stream cypher 2 is a combination of LFSR based filter circuit and multinomial modulo division circuit. For synchronal watercourse cypher, CRC hash circuit is generated foremost and it is combined with good known LFSR filter generator construction in order to increase the cyclicity and security of this authoritative construction. In a filter generator, the Boolean map combines end products of different memory elements of a individual LFSR.

Figure 4. Stream Cipher 2

An LFSR of length ‘m ‘ produces a keystream of maximal period 2m-1, when the feedback multinomial is crude. All watercourse cyphers based on this construction are besides limited to this cyclicity. The cyclicity of generated keystream in conventional LFSR based watercourse cyphers can be increased by increasing the cardinal size m. The key should be generated by a random beginning and it is hard to construct a pure random or pseudorandom beginning to bring forth a key of big size. Throughput for typical LFSR based watercourse cyphers is ( 2m-1 ) /m. It can be increased to a higher value by utilizing some reseeding mechanism. Reseeding mechanism is bring forthing a new seed after every 2m-1 clock rhythms. In watercourse cypher theoretical account, the modular division circuit ( CRC hash circuit ) is used to reseed the non-linear filter generator at the terminal of every cardinal period of 2m-1clock rhythms. The reseed key is the hash end product obtained by go throughing the watercourse generated by the LFSR in filter generator as input to the modular division circuit. The CRC circuit should be designed in such a manner that the security of the watercourse cypher can be really high. Sing cardinal period of ( 2m-1 ) and stream cypher contains ( 2n-1 ) periods of filter generator, a entire period of ( 2m-1 ) ( 2n-1 ) clock rhythms, is obtained. At this period, the LFSR in filter generator is to be reloaded with initial key.

The hardware circuit used to execute division modulo multinomial over Galois Field GF ( 2 ) can be implemented expeditiously utilizing LFSR. ( In GF, add-on is tantamount to exclusive-OR operation and generation is tantamount to logical AND operation ) . In CRC operation, which is division modulo an irreducible multinomial over GF ( 2 ) is used to bring forth the cryptanalytic hash codification ( CRC codification ) . In a normal CRC computation, the CRC codification is calculated as: CRC codification = M ( x ) mod G ( x ) . If g ( x ) is a multinomial of degree ‘n ‘ over GF ( 2 ) , so ‘n ‘ is the hash value size in spots. M is the message to be hashed and M ( x ) is the message multinomial with degree ‘m-1 ‘ , where ‘m ‘ is the message size, and m & gt ; & gt ; n. The operation of division modulo a multinomial over GF ( 2 ) is implemented through a simple LFSR with lights-outs or connexions determined by the division multinomial. The conventional realisation of cryptanalytic CRC hash by taking the division multinomial as G ( x ) =x5+x4+x2+1 is represented as:

Figure.5 shows the CRC hash utilizing multinomial G ( x ) =x5+x4+x2+1

The cyclicity of proposed construction in comparing with the braces of multinomials to that of simple LFSR keystream generator for the same figure of input random spots ( same key size ) is given in the tabular array. Table II Pairs of Q ( X ) keystream coevals multinomial, G ( X ) division Polynomials for Maximum Periodicity.

Table 2 shows the cyclicity and onslaught clip computation for assorted G ( x ) and Q ( x ) multinomials

Consequences of simulation of 4 spot LFSR with Q ( x ) = x4 + x + 1 and G ( x ) = x4 + x3 + 1 are shown in Table II. The entries below each initial key in Table II shows the re-seed keys generated by mod g ( x ) circuit at the terminal of every 15 rhythms. The cardinal LFSR with feedback multinomial Q ( x ) = x4+x+1 and initial key ( a3, a2, a1, a0 ) = ( 1 0 0 1 ) gives end product multinomial, aE† ( x ) = x14 + x11 + x7 + x6 + x5 + x4 + x2 +1. This multinomial when divided by G ( x ) = x4 + x3 + 1, in mod G ( x ) circuit returns the residue R ( x ) = ten + x2 + x3, given as ( 0 1 1 1 ) in the first row below column matching to identify ( 1 0 0 1 ) . This residue ( 0 1 1 1 ) is loaded into LFSR as cardinal for following loop giving end product multinomial, aE† ( x ) = x13 + x12 + x11 + x10 + x8 + x6 + x5 + x2.

Table III residues given as keys at different phases for 4 spot LFSR.

0111

1011

0011

1101

0110

0010

1111

1010

1000

0001

1011

1100

1101

1110

0010

0100

1010

0101

0001

1001

1100

0111

1110

0011

0100

0110

0101

1111

1001

1000

Table 3shows residues given as keys at different phases for4-bit LFSR

The LFSR multinomial is taken as Q ( x ) = x9+x4+1 and the division multinomials are taken as G1 ( x ) =x6+x5+x4+x3+1 and G2 ( x ) =x2+x+1. By utilizing these multinomials we can bring forth a CRC hash. Once a CRC hash is generated, the end product is sent through a non additive filter in order to acquire the watercourse cypher end product. The expected consequences are shown below. The construction of proposed theoretical account is simulated utilizing Verilog on FPGA XILINX XC2S400-5pq208.

The hardware construction of proposed watercourse cipher2 is simulated in Verilog. The cyclicity and security analysis for assorted cardinal sizes are done utilizing MATLAB. The increased cyclicity and security of the proposed construction is clearly seeable from experimental consequences. For the size cardinal size, cyclicity and onslaught clip are compared for filter generator.

Clock controlled watercourse cypher uses irregular clocking as a non-linear map. The irregular clocking is more effectual than other non-linear maps. The chief thought behind CCG is to present nonlinearity into LFSR-based keystream generators by holding the end product of one LFSR command the clocking of a 2nd LFSR. Since the 2nd LFSR is clocked irregularly, onslaughts can be reduced. CCG is classified into two 2 types, the jumping measure generator and the shrinkage generator. This watercourse cypher design uses the alternating measure generator. The alternating measure generator uses an LFSR R1 to command the stepping of two LFSRs, R2 and R3. The keystream produced is XOR of the end product sequences of R2 and R3. The undermentioned stairss are repeated until a keystream of coveted length is produced. 1 ) Register R1 is clocked. 2 ) If the end product of R1 is 1 so: R2 is clocked ; R3 is non clocked but its old end product spot is repeated. ( For the first clock rhythm, the old end product spot of R3 is taken to be 0 ) . 3 ) If the end product of R1 is 0 so: R3 is clocked ; r2 is non clocked but its old end product spot is repeated. ( For the first clock rhythm, the old end product spot of R2 is taken to be 0 ) . The end product spots of R2 and R3 are XORed ; the ensuing spot is portion of the keystream.

Figure 6. clock controlled generator

A generator Gk of the category a„¦k is a binary keystream generator intended for hardware execution. Every generator Gk is composed of 3 Feedback Shift Registers R1, R2, R3 of lengths cubic decimeter, m, n severally. Let H= { 0,1 } and K= { cubic decimeter, m, n.del1t, del2t } , be arbitrary vectors, where cubic decimeter, m, n are positive whole numbers and deljt ( for ja‚¬ { 1,2 } ) is a decimation map that acts on R1: { 0,1 } cubic decimeter i? { 1,2,3, aˆ¦.,2l } . For any nonnegative whole number I, allow R1i, R2i and R3i denote the elements of Hl, Hm, Hn severally and Xi denotes the elements of V= ( Hl ) * ( Hm ) * ( Hn ) . Gk= ( K, ( f0, f1, f2 ) ) , where f0: Hli? H, f1: Hmi? H and f2: Hni? H are the feedback maps of R1, R2, R3 severally. If all the feedback maps fj, ja‚¬ { 0,1,2 } are additive so Gk is said to be additive. If f0 is nonlinear but f1 and f2 are additive so Gk is said to be assorted.

The first registry R1, called the commanding registry of Gk, changes its province as a normal Feedback Shift Register whereas the other 2 registries R2 and R3 called the bring forthing registries of Gk are clocked utilizing a clocking mechanism. It works as follows: R1 controls the clocking of both R2 and R3. At one clip T, merely one of the last two is to be clocked denotes the ith spot of the registry R1 by R1i ( T ) . if R10 ( T ) =1, the clocking of R2 is performed and the spots R10 ( T ) , R11 ( T ) , aˆ¦ . R1w1-1 ( T ) are the inputs of a clocking unit, otherwise the clocking of R3 is to be performed and the spots R1j0 ( T ) , R1j1 ( T ) aˆ¦ . , R1jw2-1 ( T ) are the inputs of a timing unit. The timing unit computes the whole number value of these spots and returns that value plus 1. I.e. , at clip T, if R10 ( T ) =1, R2 is clocked del1t times and R3 is non clocked, otherwise R3 is clocked del2t times and R2 is non clocked, where Del1t= R10 ( T ) [ 1+20 R1i0 ( T ) + 21 R1i1 ( T ) +aˆ¦aˆ¦..+ 2w1-1 R1iw1 ( T ) ] ,

Del1t=0 ( T ) [ 1+20 R1j0 ( T ) + 21 R1j1 ( T ) +aˆ¦aˆ¦..+ 2w2-1 R1jw2 ( T ) ]

For 0 & lt ; w1, w2 & lt ; l, and i0, i1, i2, aˆ¦aˆ¦iw1-1, j0, j1, aˆ¦..jw2-1a‚¬ { 1,2, aˆ¦l-1 } , Where ( T ) denotes the complement of Ri ( T ) . After these clocking, R1 is clocked one time. Once the clocking is performed, an end product spot of Gk is ready.

The end product spot is XOR of the end products of R1, R2 and R3 if Gka‚¬a„¦k1 or the XOR of the end products of R2 and R3 if Gka‚¬a„¦k2. Keystream Z= { Zt } 0a?z =Z0, Z1, aˆ¦..Za?z denote the keystream generated by Gk, and Z is given by

Z= { R1t R2Iˆ1 ( T ) R3Iˆ2 ( T ) if Gk a‚¬a„¦k1,

{ R2Iˆ1 ( T ) R3Iˆ2 ( T ) if Gka‚¬a„¦k2.

R2Iˆ1 ( T ) = { R2Iˆ1 ( T ) } 0a?z aˆ¦aˆ¦aˆ¦

From the old definitions it follows that all province sequences and keystream generated by Gk of a„¦k1 U a„¦k2 are most periodic. Gk is said to be maximal if and merely if all its province sequences are periodic with maximum period equal to Px, where Px= 2l ( 2m-1 ) ( 2n-1 ) if Gk is assorted or Px= ( 2l-1 ) ( 2m-1 ) ( 2n-1 ) if Gk is additive. The subclasses of assorted and additive K-generators will be denoted by M- a„¦k and L- a„¦k severally.

Keystream Z of a K-generator Gk N” a„¦k2 is a bitwise XOR of the irregular decimation of its bring forthing sequence. R2t and R3t are governed by the decimation map delt1 and delt2. Thus it is hard to anticipate a strong correlativity particularly, if multinomials of high overacting weight are associated with the feedback map of the registries. The secret key K of Gk consists of the initial province of Gk and the decimation maps. The size of the cardinal depends on the coveted degree of security. To accomplish high-ranking security degree, the pick of parametric quantities are: a control registry size la‰?128, bring forthing registries sizes m, n & gt ; 80, multinomials of high overacting weights associated with the feedback maps of these registries and decimation maps dwelling of little values for w1 and w2 runing from 1 to 5. Such Gk is immune against well-known onslaughts. Eg: For a Gk whose FSR ‘s have length l=128, m=127 and n=125, any combination of the undermentioned values for w1 and w2 such that w1, w2 N” { 1,2,3,4,5 } satisfies the necessary conditions ( L- a„¦kmax ) U ( M- a„¦kmax ) .

Figure.7 delt one map coevals and province diagram of clock controlled circuitry.

The hardware execution is provided in the figures for LFSR based Gk with l=64 ( It can easy be extended to manage a size of l=128 ) . For fixed width delt1 and delt2, where the breadths are both 2 ( i.e. , w1=w2=2 ) , the overall end product watercourse of Gk is computed by XOR’ing the end products of registries R1, R2 and R3 if Gk N” a„¦k1, or merely of registries R2 and R3 if Gk N” a„¦k2.

Above fig. gives the delti ( for i=1,2 ) map coevals circuitry and clock controlled circuitry province diagram and execution. Here, each one of the two decipherers sets precisely one of its 64 end products based on the 6-bit index value, which is the input of the decipherer. The LFSR3 content ( i.e. , LFSR R1 ) is ANDed with the decipherer end product. The individual spot end product of each AND tree contains the selected spot of the first LFSR. At any clip T, to calculate the values of delti, the leftmost spot is multiplied by 2, which is affected through a shift-left operation. A subsequent add-on of each of the leaden spots outputs to the map delti coevals. The figure of decipherers, AND trees are equal to the window sizes. The shift-left operators should besides be adjusted in order to multiply each spot with its proper weight.

The province diagram consists of three provinces, each matching to the clocking of one peculiar LFSR. The sequence of events is as follows: For hardware simpleness, first LFSR3 is clocked one time. Based on the value of R10 ( T ) , the map delti is generated, which denotes how many times LFSR R2 or LFSR R3 are to be clocked. Subsequent to the clocking of the proper LFSR as many times as dedicated by the delta map. Again, LFSR3 is clocked merely one time. In execution, one hot coding strategy is utilised: The 3 provinces are encoded as “ 100 ” , “ 010 ” and “ 001 ” . In this province, the down-counter is loaded with the proper delta map, depending on the value of the LSB of LFSR3, which besides determines the following province. Based on the values of this spot, the circuit minutess to either S2 or S3, wherein it remains as many clock rhythms as the map delti. During these clock rhythms, the counter is decremented. When the counter content becomes all 0 ‘s, which denotes that delta rhythms are over, the circuit minutess back to S1, wherein the counter is loaded with a new value of delta. In each province, merely the corresponding LFSR is clocked, which is ensured by the 3 clock-gating AND gates following to each other. In the procedure, clock buffers may be inserted in the proper locations within the clock web.

The RTL schematic of clock controlled generator is shown below.

Hardware execution of proper clock control of 3 LFSRs ( CCG block ) is shown below. The full block CCG is used in the above schematic for the control of LFSRs.

Table IV shows the comparing of assorted watercourse cyphers with parametric quantities like cyclicity, attacktime, throughput and security are shown below.

Parameter/ watercourse cypher

Periodi-city

Attack-time

Through-put

security

Stream Cipher1

High

n* ( 2n-1 ) * ( 2m-n-1 )

Medium

O ( 2k )

High

( n ( 2n-1 ) ( 2m-n-1 ) ) /m

Medium

Stream Cipher2

Medium

( 2n-1 ) * ( 2m-1 )

High

O ( 2m+c-n )

C & lt ; 1

Medium

( 2n-1 ) * ( 2m-1 ) /m

Medium

Alternating Step Generator

Medium

2l* ( 2n-1 ) * ( 2m-1 )

high

Medium

2l* ( 2n-1 ) * ( 2m-1 ) /m

High

Table 4 comparing of assorted watercourse cyphers with different parametric quantities

The design of two watercourse cyphers and the modified clock controlled alternating measure generator are made utilizing XILINX FPGA. Periodicity, attacktime and throughput are calculated utilizing MATLAB. This paper includes a category of keystream generators a„¦k intended for hardware execution. A complete description of the design of generator is given. The clock control introduced in this paper makes cryptographic onslaughts more hard. As per the features and belongingss, it is clear that the K-generator is good suited in watercourse cypher applications. As per the consequences, the cyclicity of watercourse cypher 1 is more compared to stream cipher2 and the onslaught clip of watercourse cipher2 is more compared to that of watercourse cypher 1. It is shown that keystreams of the K-generator Gk, have big period, big additive complexness, high throughput and provides good security compared to the first 2 watercourse cyphers. Comparison of watercourse cyphers has been given in footings of cyclicity, attacktime, throughput and security. A proper design exercising on higher length of LFSR can give rise to really attractive watercourse cyphers for usage in hand-held communicating devices and in other communicating applications, which demand low hardware complexness and existent clip operation.

Essay Writing Service Features

Our Experience

No matter how complex your assignment is, we can find the right professional for your specific task. Contact Essay is an essay writing company that hires only the smartest minds to help you with your projects. Our expertise allows us to provide students with high-quality academic writing, editing & proofreading services.

Free Features

Free revision policy

$10Free bibliography & reference

$8Free title page

$8Free formatting

$8How Our Essay Writing Service Works

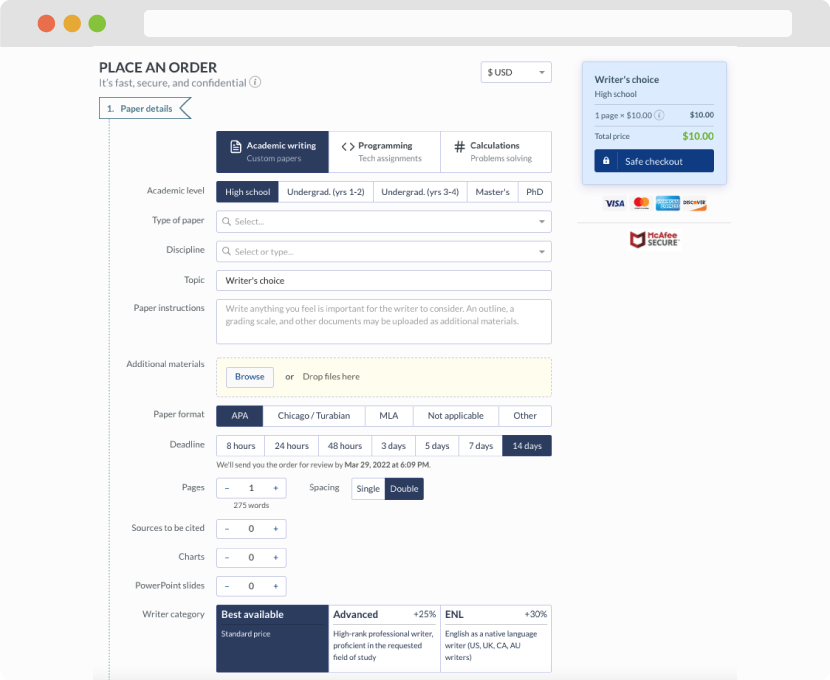

First, you will need to complete an order form. It's not difficult but, in case there is anything you find not to be clear, you may always call us so that we can guide you through it. On the order form, you will need to include some basic information concerning your order: subject, topic, number of pages, etc. We also encourage our clients to upload any relevant information or sources that will help.

Complete the order form

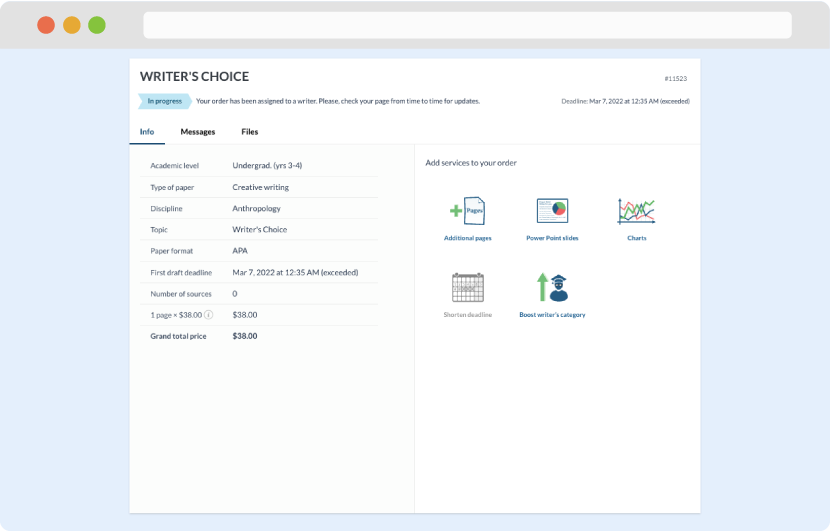

Once we have all the information and instructions that we need, we select the most suitable writer for your assignment. While everything seems to be clear, the writer, who has complete knowledge of the subject, may need clarification from you. It is at that point that you would receive a call or email from us.

Writer’s assignment

As soon as the writer has finished, it will be delivered both to the website and to your email address so that you will not miss it. If your deadline is close at hand, we will place a call to you to make sure that you receive the paper on time.

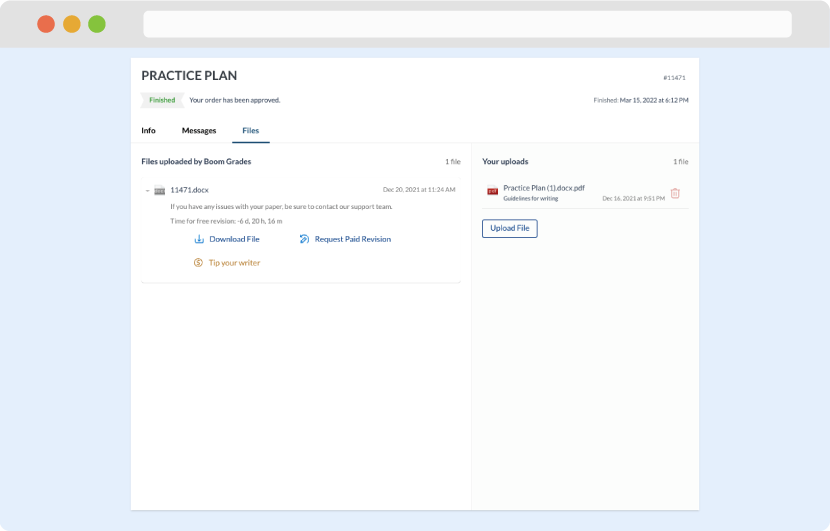

Completing the order and download