Quantum dot Ce llular Automata (QCA) is one of the developing patterns in the field of nanotechnology, which beats the

constraints of CMOS innovation. QCA can be utilized to structure m emory circuits. Static Random Access Memory (SRAM)

is one of the appealing utilization of QCA Innovati on. The proposed plan and simula tion of memor y cell dependent on QCA

with minimum area and complexity.

This paper presents the design and simul ation of multiport SRAM in QC A with least

number of majority gates and it will be simulated using QCA Designer Tools .

SRAM based QCA execution has been contrasted

and CMOS innovation utilizing Xilinx. The comparison results Show that the QCA memory circuit provides high efficiency in

terms of area, complexity and power consumption. QCA can be used to design memory circuits. Static Random Access Memory

(SRAM) is one of the attractive application of QCA Technology. The proposed design and simulation of memory cell based on

QCA with minimum area and complexity. This paper presents the design and simulation of multiport SRAM in QCA with

minimum number of majority gates and it will be simulated using QCA Designer Tool. SRAM based QCA performance has

been compared with CMOS technology using Xilinx.

Keywords:QCA;Majority gate; Multiport memory

1. Introduction

Feature size in CMOS has decreased after a drawn –

out period of time; regardless, a couple of

requirements still exist. This has caused the s nappy

enhancement of molecular plans on the nanoscale.

QCA is one of the nanotechnology has been as of late

perceived and it is relied upon to accomplish low zone

and power utilization and high exchanging pace.

QCA

has no voltage source and the situation of electrons

decides the consistent qualities [2]. Static random

access memory (SRAM) speaks to an appealing use of

the QCA innov ation. Its structure is entirely

reasonable for creation at the nanoscale [3].

[4]Implemented memory as parallel read/sequential

compose. The fundamental target of this paper is a

handy reduced multiport Memory cell in QCA. The

region and postponement of t he QCA -based SRAM

cell displayed in this paper was contrasted and the

SRAM cell dependent on CMOS and our proposed

structure of multiport memory utilized in the plan of

SRAM cell has proficiency as far as region and

multifaceted nature when contrasted with [1]. The

outcomes demonstrates that the proposed SRAM cell

performs with a base expended zone. The rest of th is

1.1. Review of QCA Cell

QCA cell is a square shape with four Quantum

spots situated at its corners. There are two electrons in

every cell that can burrow between two quantum dots

in a cell, however they can’t burrow between two cells.

Initial one demonstrates a standard QCA cell with four

specks at the corner. The polarization speaks to

rationale expresses that twofold rationale 0 and paired

rationale 1. On the off chance that the two electrons

adjust in the lower left and upper right dots, it speaks

to rationale 1 state speaks t o second figure. On the off

chance that the two electrons adjust in the upper left

and lower right specks, it speaks to rationale 0 state in

third figure. Figure 1. (a) QCA cell portrayal (b) Cell

polarization = +1 (Rationale 1) (c) Cell Polarization =

– 1 (Rationale 0).

1.1.1. Clocking in QCA

A single QCA wire and the condition of the variety

of cells of a similar wire in an alternate clock zone are

appeared. The four clock zones of QCA are

demon strated as Clock 1: Green, Clock 2: 15 Pink,

Clock 3: Blue and Clock 4: White. The four clock

periods of QCA are: 1) switch; 2) hold; 3) discharge;

and 4) unwind. In the Switch period of the clock, the

QCA cells are at first unpolarized and their potential

obstructions are low. Amid the switch stage, the QCA

cells energize and boundaries turn out to be high; in

this stage calculation happens. Amid the hold stage,

obstructions are held high. In the discharge stage,

obstructions turn out to be low and the QCA cells are

unpolarized. In the loosen up stage, obstructions stay

low and the QCA cells remain unpolarized. Fig. 2

1.1.2. Inverter

A standard structure of the QCA inverter in which

the information is given at one of the closures and the

altered yield is acquired at the opposite end. The input

wire parts into two parallel wires, and due to Columbia

fascination it enraptures the cell put toward the finish

of these wi res on the right hand side to the contrary

1.1.3. Majority Gate

A fundamental component of QCA circuit is

Majority gate; as majority logic can be utilized for

executing any logical function as opposed to utilizing

Boolean logical operators. A two input AND function

can be a ctualized by a three input majority gate by

settling one of its c ontributions as a logical zero,

though on the off chance that one input of a majority

gate set to legitimate one it acts like a two input OR

functi on. The essential QCA logic comp onent is a

majority gate as shown in fig. 3.It produces a yield of

1.2. QCA Memory cell

In this section, an outline of QCA memory

structures is presented. These structures depend on the

memory -in movement worldview by which the

estimation of the put away information is moved

through various cells in a closed loop spanning at least

four clocking zones. These structures have diverse

highlights, for example, number of bits stored in a

loop , get to type (sequential or parallel) and cell plan

for the memory bank. The parallel design is like a

customary CMOS based memory engineering. The

fundamental memory cell of this engineering is

appeared in Fig. 3. The information bit is put away in

a cir cle, until the WR/RD control flag is low.

Whenever WR/RD is raised high, at that point the

information bit is put away on the up and up. The circle

must be actualized utilizing all zones of the four s tage

adiabatic switching technique for the clock , thus

allowing the motion of the stored bit . Beginning from

the basic cell, a variety of memory cells can be

actualized utilizing similar structures utilized in the

plan of CMOS memory banks. In a QCA pipelined

framework, this enables the put away an incentive t o

be protected on the up and up until the compose mode

happens. The privilege AND gate is called an enable

gate and wo rks freely from rest of the circuit. Despite

whether one is in the read or write mode, the enable

gate yields the stored value when EN is ‘1’. This

demonstrates the memory cell is chosen to be perused.

Something else, when EN is ‘0’, the yield is ‘0’, which

implies that the memory cell isn’t chose to be perused.

The circuit schematic for proposed QCA memory cell

is appeared in fig. 3.In the above figure, disclose s

SRAM keeps on being a fundamental and important

memory innovation. It demonstrates the technology of

memory cell. In th e memory cell when EN = 1, output

is enabled and when EN = 0, output = 0. Whenever

R/W = 1, the read state is ena bled and the D value is

saved in the memory circle. Whenever R/W = 0, the

read state is enabled and th e saved bit is placed on the

2. Implementation of multiport memory in QCA

2.1. Dual port memory

This section presents the proposed structure of dual

port SRAM and depicts their block diagram. The

design of multi -port SRAM requires more than one Fig. 4 . Block diagram of dual port memory

Port . Here in these case mainly shows the gate -level

design of dual port memory. Our proposed structure of

dual multi -port which is necessary for designing the

one data i/p port and two data o/p port memory. Do not

use abbreviations in it. It requires seven i/p ports and

it is efficient in terms number of cells and area when

compared to secondary memory.First dual port gate

level architecture is designed in QCA.

Fig. 5. Design of dual port memory in QCA

2.2. Memory of Quad port

The quad port memory cell is designed to obtain the

structural difference in QCA. Mainly, there are three

cases need to identified to design a multiport memory

using tri -state logic gate. First is writing operation,

second is read operation and last operation is w/r

inconsistence. The theoretically semaphore concept i s

realized to resolve the problem. But practically it is

finding out to overcome the problem in current

technology research. It is very di fficult to say that in

between three cases which priorit y is more important

Fig. 6. Design of Quad port memory in QCA

3. Multiport gate level architecture in CMOS

(Xilinx) technology

3.1. Design of dual port memory

The result of the QCA designer tool is compared to

Xilinx tool (which is based on the CMOS technology)

in terms of area, cells and gates used in QCA

technology. The more efficient technology used in

Xilinx, that can be helped to find out the solution to

overcome the r/w inconsistence and priority resolver.

This paper have two main objectives: i ) reduced

consumed area ii ) achieving minimum complexity.

3.2. Quad port memory in Xilinx

In Xilinx tool quad port memory design is

basically dependent on the gate level architecture. The

approach towards the architecture which is

inconsistent with data flow and power dissipation of

the entire CMOS technology. Fig. 8. Design of Quad port memory

4. Simulation and results

The design and simulation of a dual port as well as

Quad port SRAM in the QCA technology are

presented in this paper. The proposed tri -state

multiport memory is a flexible and powerful structure

using Programmable logic and interconnections. The

design is significantly improved because this memo ry

has a 32 -bit width. In comparison with other studies,

the presented memory cell acts as a pipeline that

decreases delays and increases operating speed. The

designs can be implemented using the QCA Designer

and simulated by the QCA Designer software tool and

also simulated using the Xilinx RTL encounter tool.

The results showed that the proposed QCA based dual

port performs a task with reduced area and complexity

in terms of number of cells when compared to CMOS

Fig. 9. Simulation of dual port memory in QCA

Fig. 10. Simulation of dual port memory in Xilinx

Summary of data obtained from the simulation of dual port and quad port memory in QCA as well as Xilinx

QCA Technology using QCA designer tool CMOS technology using Xilinx RTL

Sl

no.

1 Dual port 0.06µm 2 53 9.70?10 20 32m 2 109 1.237

2 Quad port 0.22µm 2 183 9.73?10 20 127m 2 280 2.089

Fig. 11. Simulation of dual port memory in QCA

Fig. 12. Simulation of Quad port memory in Xilinx

5. Conclusion

The results showed that the proposed QCA based

SRAM performs a task with reduced area and

complexity in terms of number of cells when

compa red to CMOS based SRAM.TABLE I shows the

comparison between QCA and Xilinx tool. It is a

significant improved in terms of area about 0.22 for

quad port and 0.06 for dual port . TABLE I shows that

our p roposed structure of multiport SRAM has

efficient in terms of area and complexity. Thus our

proposed paper have overcome the problems in CMOS

technology on nanoscale. It is expected that the

reduction method presented in this work would

produce significant hardware savings for many future

The authors would like to express their thanks to

the Department of Computer Science and Eng ineering,

Adams University , K olkata and the Department of

Electronics and Communication Engineering ,

Durgapur Institute of Advanced Technology and

Management, Durgapur, for the constant infrastructure

support. The authors also greatly acknowledge the

suppo rt of others faculty member of Department of

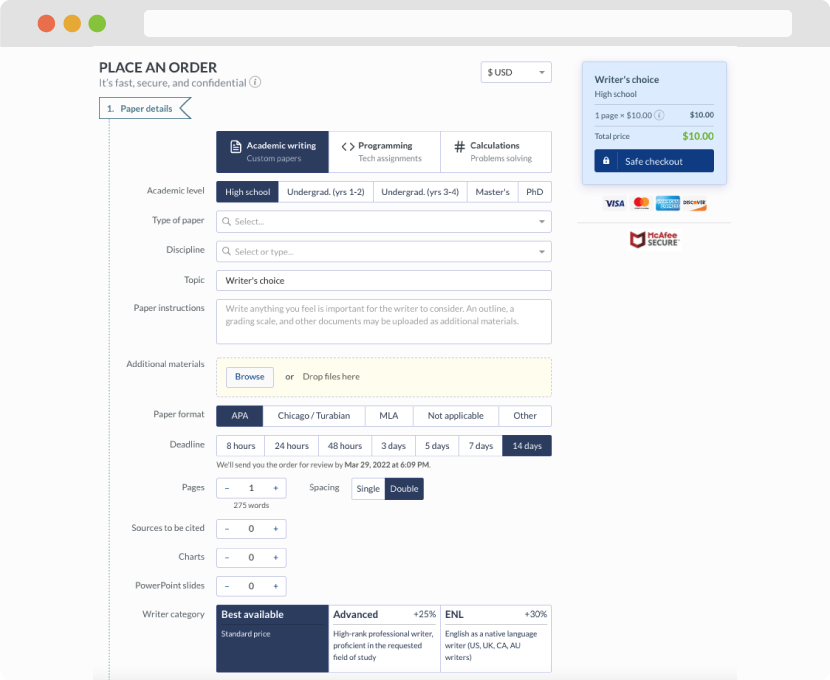

Essay Writing Service Features

Our Experience

No matter how complex your assignment is, we can find the right professional for your specific task. Contact Essay is an essay writing company that hires only the smartest minds to help you with your projects. Our expertise allows us to provide students with high-quality academic writing, editing & proofreading services.

Free Features

Free revision policy

$10Free bibliography & reference

$8Free title page

$8Free formatting

$8How Our Essay Writing Service Works

First, you will need to complete an order form. It's not difficult but, in case there is anything you find not to be clear, you may always call us so that we can guide you through it. On the order form, you will need to include some basic information concerning your order: subject, topic, number of pages, etc. We also encourage our clients to upload any relevant information or sources that will help.

Complete the order form

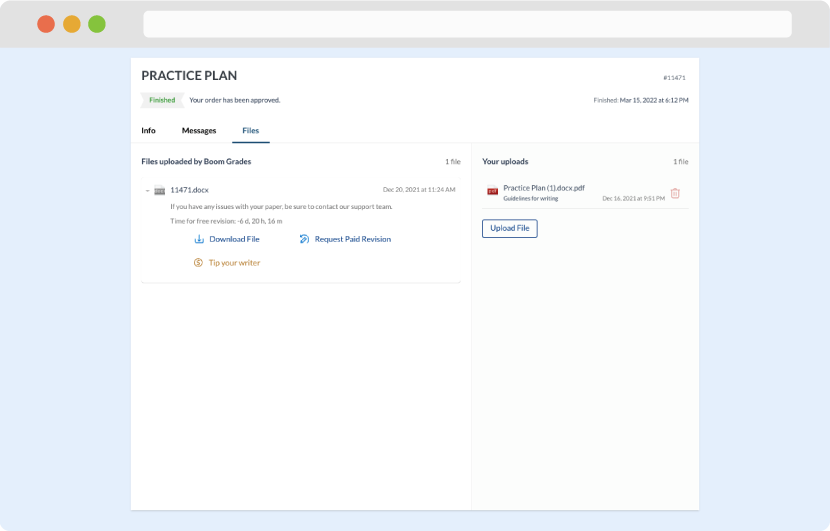

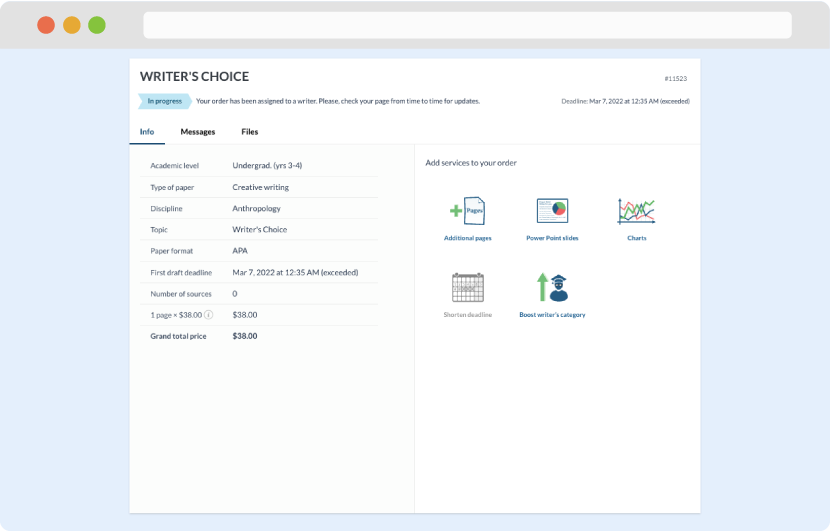

Once we have all the information and instructions that we need, we select the most suitable writer for your assignment. While everything seems to be clear, the writer, who has complete knowledge of the subject, may need clarification from you. It is at that point that you would receive a call or email from us.

Writer’s assignment

As soon as the writer has finished, it will be delivered both to the website and to your email address so that you will not miss it. If your deadline is close at hand, we will place a call to you to make sure that you receive the paper on time.

Completing the order and download