CPU must hold compatibility with the memory in the computing machine system. Memory can non increase the velocity of the processor nevertheless it can assist the processor increase its public presentation. If the CPU does n’t acquire the informations it requires, it would sit idle blowing CPU clock rhythms that would diminish the overall throughput and executing of the procedures. If informations demands to be accessed to and from difficult disc which is slower as compared to the chief memory, more and more rhythms are wasted diminishing the efficiency of the system.

Conclusion- For better public presentation of the system, faster plan executing and proper CPU use the compatibility between CPU and memory is required.

A computing machine employs RAM french friess of 256*8 & A ; ROM french friess of 1024*8. The computing machine society system needs 2K byte of RAM & A ; 4KBYTE of ROM, & A ; 4 interface units. Each with 4 registries. A memory mapped I/O constellation is used. The 2 highest order spots of the reference coach are connected with address 00 or RAM and 01 for ROM & A ; 10 for interface.

How many RAM & A ; ROM french friess are needed? Pull a memory reference map.

2 kilobit of RAM required i.e. 2×1024 ( bytes ) =2048 bytes ( Since 1 kilobits =1024 bytes )

RAM = = 8 french friess ; and

4kb of ROM is required i.e. 4 ten 1024 = 4096 bytes

Therefore ROM = = 4 french friess ; and

There are 4 interfaces each holding 4 registry, So entire no. of registries is 4×4=16 registries ;

Component

Address

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

Random-access memory

0000-07FF

0

0

0

0

0

3×8 decipherer

ten

ten

ten

ten

ten

ten

ten

Read-only memory

4000-4FFF

0

1

0

0

2×4 decipherer

ten

ten

ten

ten

ten

ten

ten

ten

ten

ten

Interface

8000-800F

1

0

0

0

0

0

0

0

0

0

0

0

ten

ten

ten

ten

Cache Coherence-

Caches allow greater public presentation by hive awaying often used information.

In multiprocessing system, each processor is provided with its ain cache and they all portion the same memory or address infinite so it is possible for more than one processor to entree a information point at a clip. What if one processor updates the informations point without informing the other processors, incompatibilities may ensue and do wrong executings and the job of incompatibilities is known as Cache Coherence in calculating.

The coherency of caches is obtained if the undermentioned conditions are met. However these read and write operations are said to be one after another and this is non possible due to memory entree latency and a write by first processor may non be seen by a read from 2nd processor if the read is made within a really little clip after the write has been made.

Case 1 Case 2

Processor P1 reads memory location X and so writes back to same location X while no other processor is non accessing the memory location X.

Processor P1 reads and so processor P2 writes to and from same location X and presently the location would return value written by processor P2 merely.

Processor P1 and P2 writes to same memory location X in a sequence and presently the value returned would be decided as per the sequence.

Mechanisms-

Bus Snooping- In Bus Snooping each cache is connected through the same coach and it is where every CPU knows who has a transcript of its cached information. So each CPU tickers continually for write activity concerned with informations references which it has cached. This assumes that all communicating can be seen by all. However it is far more complex to implement.

Directory Based Approach- In a directory-based system, the informations being shared is placed in a common directory that preserves the coherency connecting caches. The directory Acts of the Apostless as a filter through which the processor must inquire mandate to make full an entry from the primary memory to its cache. When an entry is distorted the directory either updates or invalidates the other caches with that entry.

The MESI protocol is the best suited protocol to avoid cache coherency, where M stands for MODIFIED, E stands for EXCLUSIVE, S stands for SHARED and I stands for INVALID.

Write Back Cache-

Cache uses two attacks to compose informations back to chief memory.

It is the simplest 1 in which all write all operations are made to the chief memory every bit good as to hoard ; guaranting chief memory is ever valid. Any other CPU- cache faculty can supervise traffic to chief memory to update the informations in its ain cache, but ever consequences in significant memory traffic.

It minimizes memory writes. In write back method alterations to informations in the cache are n’t copied to the cache beginning until perfectly necessary. It is besides known as transcript back cache.In write back updates are made merely in the cache. When an update occurs UPDATE spot are set associated with the slot and when the block is replaced it is checked whether the UPDATE spot is set or non. If it is set so informations is written back to chief memory.

For Example- Intel processors since the 80486 utilizations back hoarding.

Problem with this sort of execution is that public presentation betterment comes with a little menace that informations may be vanished if the system clangs and more complex circuitry.

Onboard Cache-

Cache is a portion of multi-level storage scheme which is used to increase the public presentation of CPU by supplying a span in between the slower memory RAM and CPU. The cache that is the portion of the CPU is known as off-board cache and the cache which is present on the motherboard is known as on-board cache. Generally L1 cache is referred as off-board and L2 is known as on-board. Sometimes L3 cache is besides present on the motherboard along with L2. Now a twenty-four hours ‘s specific CPU sellers incorporates L2 as a portion of CPU and L3 on motherboard.

Execution of Cache-

In Cache, latency demands to be decreased and hit rate demands to be increased. Larger caches have better hit rates but longer latency. To turn to this job, many computing machines use multiple degrees of cache. The smaller and faster one is L1 cache built inside the CPU known as on-chip. If CPU needs informations it foremost checks in L1 ; if it hits the processor returns at high velocity.

If the smaller cache girls, the following larger cache ( L2 ) is checked, and so on, before external memory is checked. As the latency difference between chief memory and the fastest cache has become larger, some processors have begun to use every bit many as three degrees of on-chip cache. For Example- Intel ‘s Xeon MP Product code-named “ Tulsa ” , AMD Phenom II ( 2008 ) , Intel Core i7 ( 2008 ) uses incorporate L3 cache. However Cache can be implemented by utilizing Direct Mapped, Associative Mapping or Set-Associative Mapping.

Virtual Memory-

For the executing of plans memory required is more than what is really present. So, the technique used to get the better of this size restriction is Virtual Memory which is semblance of memory non physically present. The intent is to let multiple plans portion same memory leting dividing up of plan into smaller pieces that can be loaded into different parts of memory whenever infinite can be found.

Execution of Virtual Memory-

It is implemented utilizing two techniques- one is Demand Paging and other one is Demand Segmentation.

CPU generates reference which is non physically present. These are the plan addresses referred to as logical references, they do n’t hold any being outside the plan, the existent memory references are known as physical references. These practical references are mapped or interchanged to its matching physical reference through a procedure known as function. A page tabular array or look up tabular array is maintained for this intent.

In Demand paging, valid-invalid spot strategy is used in which a valid-invalid spot is associated with each page. 1 for the page in memory and 0 for non present in memory. During address interlingual rendition if spot in entry is 0 the page mistake occurs. In practical memory procedure are divided into balls of equal size known as pages and balls of memory in which pages are loaded are known as frames.

In Demand Segmentation each row of the search tabular array contains a starting reference for a logical block of memory, together with the size of the block and a corresponding get downing reference in physical memory. Paging and Segmentation operates both the same.

Problem of Fragmentation-

Fixed Memory Partitioning- Operating system occupies fixed part of chief memory and dividers are created for multiple procedures but non of same size, so there will be wastage of memory. In most instances the procedure will non get memory provided to it.

Variable Memory Partitioning- In variables-size dividers, the memory allocated is every bit much it is required by procedure. However when procedures are swapped in, little holes are created taking to job of atomization. Compaction is done to work out job, but it waste CPU clip.

In Virtual Memory demand paging method is implemented, in which memory is partitioned into equal balls that are comparatively little, and each procedure is divided into little fixed size balls of some size. The lists of the frames that are free are maintained by the operating system. As the size of the pages and frames are same so suffer less atomization job.

The Memory Hierarchy

The design restraints on a computing machine ‘s memory can be summed up by three inquiries: how much memory is available, how fast it is and how much it will be? Following are the relationships between these tradeoffs-

Smaller entree clip, greater cost per spot.

Greater capacity, smaller cost per spot.

Greater capacity, greater entree clip.

Access Time Increase

Transportation Rate DecreasesCPU Registers

Cache

Cost per/bit Decreases

Capacity IncreasesRAM

Magnetic Disk

Storage Medium

Average Access Time

Capacity

( Min. )

( Max. )

CPU Registers

15 nsec

30 nsec

Cache

50 nsec

100 nsec

Random-access memory

75 nsec

500 nsec

Magnetic Disk

10 millisecond

50 millisecond

Benefits of Memory Hierarchy-

Memory hierarchy helps in increasing the public presentation of processor, without hierarchy, faster procedure wo n’t assist and all clip waiting on memory, It provides a big pool of memory that costs every bit much as the inexpensive storage near the underside of the hierarchy, but that serves informations to plans at the rate of the fast storage near the top of the hierarchy. It provides a faster entree of informations stored in the memory. If it is understand how the system moves data up and down the memory hierarchy, so application plans can be written so that informations points are stored higher in the hierarchy, where the CPU can entree them more rapidly.

Addressing manners impacting public presentation of system-

It simplifies the memory mentions, produces variable length direction format and direction manipulates operands in memory straight. It adds convenience and flexibleness to hold manners of addressing, and it allows a big scope of addressable memory while utilizing a sensible figure of spots. Addressing manners make it easier to compose certain type of plans such as cringles that uses an index to turn to different entries in a tabular array or array. For Example- Indexed Addressing. Now a twenty-four hours ‘s computing machine allows coder accessible registries that manipulate informations straight between registries.

Essay Writing Service Features

Our Experience

No matter how complex your assignment is, we can find the right professional for your specific task. Contact Essay is an essay writing company that hires only the smartest minds to help you with your projects. Our expertise allows us to provide students with high-quality academic writing, editing & proofreading services.

Free Features

Free revision policy

$10Free bibliography & reference

$8Free title page

$8Free formatting

$8How Our Essay Writing Service Works

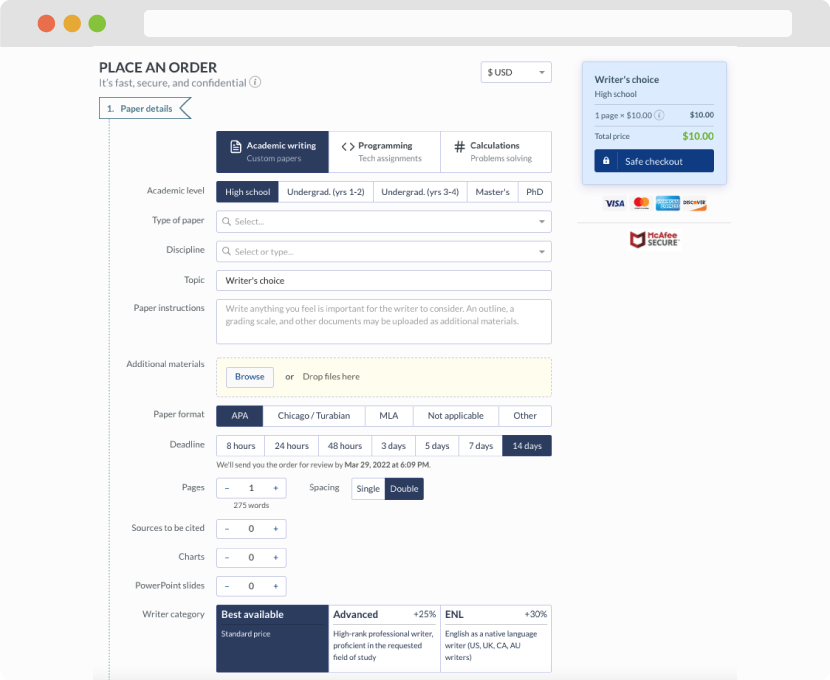

First, you will need to complete an order form. It's not difficult but, in case there is anything you find not to be clear, you may always call us so that we can guide you through it. On the order form, you will need to include some basic information concerning your order: subject, topic, number of pages, etc. We also encourage our clients to upload any relevant information or sources that will help.

Complete the order form

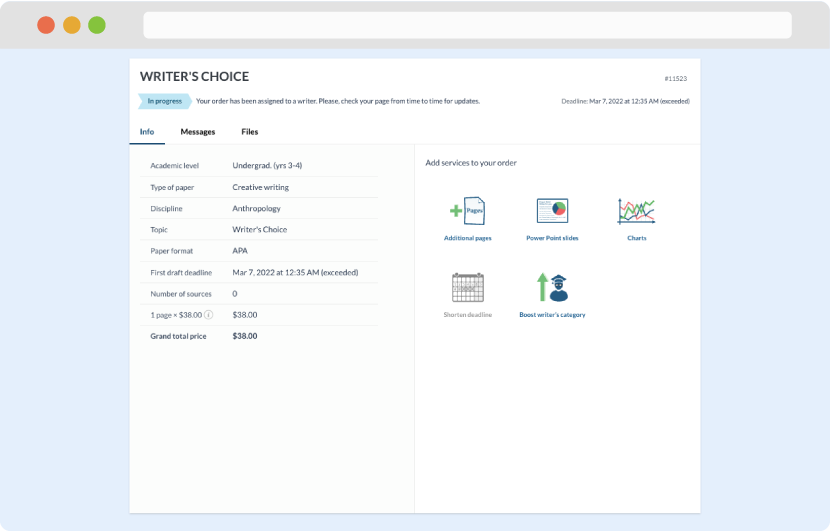

Once we have all the information and instructions that we need, we select the most suitable writer for your assignment. While everything seems to be clear, the writer, who has complete knowledge of the subject, may need clarification from you. It is at that point that you would receive a call or email from us.

Writer’s assignment

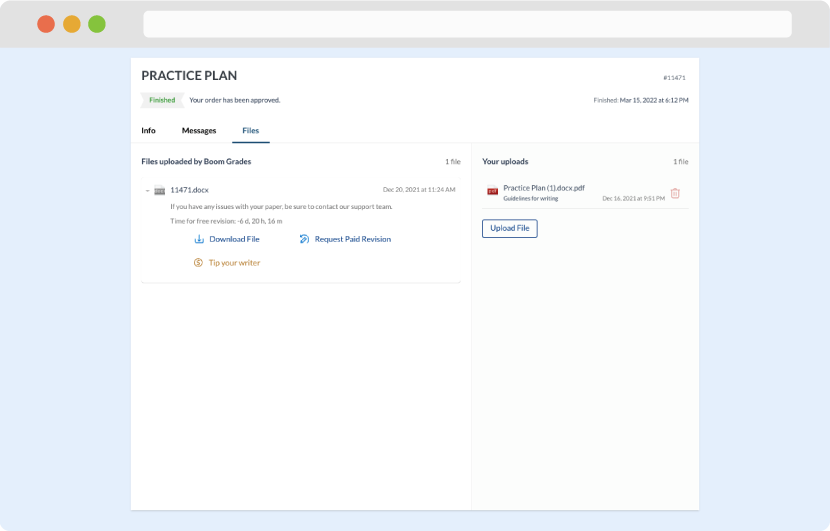

As soon as the writer has finished, it will be delivered both to the website and to your email address so that you will not miss it. If your deadline is close at hand, we will place a call to you to make sure that you receive the paper on time.

Completing the order and download