Abstract— An act which is to a deliberate control of the incorporated circuit or its state, with an aim to incite a mistake inside the coordinated circuit with the end goal to move the gadget into an unintended state. The objective is to get to security-critical data or to disable internal protection mechanisms. This is a survey paper based on few current trends of hardware only schemes in which value prediction is used to the maximum extent in representation, expression and in system design to mitigate fault attacks in general purpose microprocessors. Here we will describe challenges that cause the fault attacks and future directions and a comprehensive list of references to assist researchers. This survey mainly talks on two approaches; value prediction(VPsec) and Simon implementation against intelligent fault attacks.

Keywords: fault attacks; Value prediction bits; Simon; fault detection; pipeline; Ciphertext.

I. Introduction

Security is a very important concern for developing the secured and trustworthy microprocessors and embedded systems. Slowly these unintentional fault attacks have started to intentional faults like an example called The Bellcore Attack[BDL97][1]. At the time when they proposed the Bellcore, it was theoretical but later with the improvements in the technology they put this attack in practice. Fault attacks which occur intentionally are different from the random faults which are caused by the environmental conditions or manufacturing defects or by a radioactive environment with respect to fault location, injection timing and faulty vector size [2]. So with these factors in mind the existing fault detection methods which are designed for random faults may not be applicable to handle these intelligent fault attacks. First, we will see a few existing approaches and their limitations before we get into the details of the VPsec and Simon techniques to mitigate the fault attacks. They are explained here in the following section briefly.

This paper is organized as the shown following, section II shows the previous work and approaches followed for mitigating the fault attacks followed by section III shows techniques to mitigate the attacks and section IV explains and followed by a conclusion

Hardware-based mitigations generally replicate a certain part of hardware like registers which can be used for repeating computation s and verify these computation results using a specific hardware part. Whereas software-based approaches give more flexibility since they do not need any hooks in hardware. Earlier techniques on software-based ones impact the algorithm level or instruction level [3]. These algorithm level mitigations duplicate the algorithm execution and then outcomes of both the executions are compared to verify integrity. Similarly, ISA level mitigations attempt to counter the faults by duplicating instructions, repeating executions, and then notes the similarity or dissimilarity between the original instruction and the redundant one[4].

However, both these software based and hardware based are very expensive ones in terms of performance overhead and energy increase.

Figure 1. Fault Attacks [5]

II. related work

There are few other existing approaches which consider the scenarios of faults which occur with the cipher implementation. Since all these attacks are intentional we need a strong fault detection mechanism in order to avoid the intelligent fault attacks. Figure 2. shows the attack which is caused by injecting the input in intermediate state registers. This happens here since both the data paths get the same input which is a faulty one. As they receive the same faulty input in both data paths the difference is not noticed at the comparison stage. As a result, a faulty ciphertext which is received as input can bypass the fault detection.

Figure 2. Fault detection methods against fault attacks. (a) double modular redundancy (DMR) (b) inverse function (c) permutation and (d) masking [2]. Here F(.) used to represent one round function for the cryptographic algorithm.

Each approach has its own drawbacks for symmetric fault injection. Here symmetric faults i.e., intelligent faults means two faults which are injected in two data paths of encryption unit with the idea that the two faults will cancel out the effect of fault detection stage. In figure 2(a) if the fault attack is performed at the same time and the same location on that two same F (.) functions DMR will fail. In figure 2(b) inverse function is designed with symmetric architecture will also fail if the recovered state i is modified before the comparison takes place. In figure 2(c) permutation can also fail since the input bits may share the same logic. In figure 2(d) it uses the property XOR. Because of this property, even this scheme cannot detect the fault if the fault bits and injected locations are same. This problem can’t be solved even if the order of masking is extended.

Get Help With Your Essay

If you need assistance with writing your essay, our professional essay writing service is here to help!

Essay Writing Service

III. Techniques to mitigate fault attacks

A. Value prediction for security(VPsec)

In the proposed framework [4], value prediction is the main scheme which uses to build proposed value prediction for security(VPsec) framework. Any scenario of fault attacks mentioned in [2] can be mitigated by the proposed technique. Basically, fault attacks can be classified into two scenarios, one is to produce fault data values and the latter is to predict fault data. The architecture proposed by [4] includes three basic blocks and they are valued prediction block, block for logic detection and logic of reaction. The first block is used to predict accurate value, the second block compares the predicted value and produced value, when comparison detects large variation then the third block is used to mitigate the discrepancy. The fault attacks can occur by an attacker in two ways, first one is to incorporate faults into data values through data path and the second one is to include faults into value predictor block to produce fault predict values. In conventional systems value prediction depends on produced value from data cache whereas the proposed system depends on predicted value from predictor logic block. In this case, value prediction is used to reduce fault attacks in microprocessors. In VPsec system, the probability to choose predicted value depends on confidence and accuracy of prediction value. Also, one major difference between the proposed and conventional system is the way of recovery of original data. The way of recovery is to execute consumer instruction again in conventional approach whereas in VPsec approach both consumer and producer instructions are executed again.

when faults include in value predictor block, new hardware elements like producer status registers(PSR) used to keep track of instructions of the producer. In the initial stage, PSR value is zero and its size is an 8-bit length. when producer instruction is executed back again this bit is set to one and this bit keep track of faulty instruction executed by an attacker. Whenever new scheme encounters non-zero value in PSR registers, the situation seems to not trustworthy and unusual. Now recovery has to be done in order to correct the faulty bit. The recovery schemes to reduce faults in VPsec approach as follows.

Algorithm VPsec_Value_Prediction

if prediction confidence > = 99% or prediction value > = 99%

then

produce predicted value = TRUE

produced value = predicted value

recovery_action = NIL

else if (prediction confidence < 99% && prediction confidence > 90%) or (prediction value < 99% && prediction value > 90%) then

produce predicted value = FALSE

recovery_action = True

Perform flush, fetch-again and execute producer value.

Case 1: when PSR bit equals to zero and prediction accuracy is high then nothing needs to be done.

case 2: when PSR bit equals to zero and prediction accuracy is low then recovery options as mentioned above like flush, fetch-again and execute producer value can be done.

case 3: when PSR bit is equal to one or non-negative then it is a sign for the unusual case an attacker is observing the behavior of a microprocessor. Now, produce wrong data and continue the program execution with wring input value and show to an attacker [6].

In all these three cases new scheme handled very well, and the program execution has not been halted anywhere.

CNT represents the PSR value for the value predicted instruction

Figure 3. Basic blocks of VPsec [4]

The proposed design[4] comprises three basic blocks to implement value prediction. (1) value prediction block (2)detection block and (3) Reaction block. The first block is a valued prediction and this block is a set of predictors like context based predictors[8] and value predictors[7]. These predictors work at a time for single instruction and provide various predictor values. Finally, choosing one predictor value is based on a voting system. Majority of predictors precisely choose the same predictor value which makes the easy job to predict a value. Detection block is the second basic block of VPsec architecture. This block compares the produced value which is the outcome of a data block with predictor value the outcome of predictor value block. This result is passed to the next block. Reaction block is the final block in VPsec architecture which estimates the use of PSR register and verifies prediction confidence.

Based on the outcome, this block performs optimum recovery scheme from three various recovery schemes mentioned above.

B. SIMON Implementation against intelligent Fault Attacks

In the proposed approach [2] two intermediate registers can be used to identify the fault injection by an attacker. This approach verifies both registers for data equality and detects any fault data in any one of the register. Hence identified fault register can be discarded and keep original data from the second register. This new scheme overcomes the problem with existing techniques which use only one intermediate register. In this approach, an attacker has to keep track of both the registers at some point of time and inject fault data value. This has very less probability to manipulate both the registers.

IV. evaluation

Table 1. Area and power consumption comparison [2]

The SIMON approach was evaluated for fault rate and cost of hardware with respect to existing methods DMR [9], DuoMask, permDeperm[10] [11] and inverse function[12]. Firstly fault rate is calculated as the total number of fault detections on an overall number of tests. This is a very important measure to identify the effectiveness of an approach. If an attacker performs multiple fault activities on a chip then fault rate value will be high. The main aim of the proposed algorithm is to reduce the value of the fault rate. Secondly, designed microprocessor occupied less amount of area when compared with the existing approaches and power consumption was slightly greater than very powerful algorithm[12]. Overall, proposed technique occupied 5% greater area and 6% high consumption of power when compared to very powerful technique [12].

VPsec approach was evaluated on a design of prediction along with existing approaches like OpenSSL[13], SPEC CPU2017[14], Terasort, SPEC CPU2006 [15] and SPMV [16]. During the evaluation process, multiple fault attacks have been done on all the above approaches and tested their confidence, coverage, accuracy. After testing, the proposed VPsec approach shown very good results when compared with other approaches. VPsec approach was robust and did not impact with any of the attacks during simulation.

V. Conclusion

Security is a very important factor for both embedded systems and general-purpose microprocessors. In this paper, we mainly see few existing approaches for countermeasures of fault attacks and their limitations. Also, we discuss regarding the VPsec and Simon approaches for mitigating the fault attacks to general purpose processors and embedded systems. A new hardware technique called VPsec works in the following manner. It first detects the occurrence of faults, then has the logic to react against the occurrence of faults and has new security aware reactions. With this technique even, performance can be improved by using value prediction. And similarly, with the Simon approach, we have a new fault attack algorithm which combines the masking techniques and operand permutation. This is the first technique to provide the closed-form expressions of the depermutation and demasking functions.

VI. Future Work

VPsec needs to monitor the status of all the pipeline instructions, number of PSR registers required to match the number of entries in the reorder buffer. With this feature, VPsec has a very less area and power overhead and increases a minute power consumption [5]. The later technique i.e., Simon’s approach gives an area overhead of 5% and 6% more power consumption than the most efficient algorithm. So, there is a chance for researchers to develop even more efficient techniques in the future [2].

References

[1] Giraud C., Thiebeauld H. (2004) A Survey on Fault Attacks. In: Quisquater JJ., Paradinas P., Deswarte Y., El Kalam A.A. (eds) Smart Card Research and Advanced Applications VI. IFIP International Federation for Information Processing, vol 153. Springer, Boston, MA

[2] J. Dofe, J. Frey, H. Pahlevanzadeh and Q. Yu, “Strengthening SIMON Implementation Against Intelligent Fault Attacks,” in IEEE Embedded Systems Letters, vol. 7, no. 4, pp. 113-116, Dec. 2015.

doi: 10.1109/LES.2015.2477273

[3] H. Bar-El et al. The sorcerer’s apprentice guide to fault attacks. Proceedings of the IEEE, vol.94, no. 2,pp.370-382,2006

[4] R. Sheikh, R. Cammarota, and W. Ruan, “Value prediction for security (VPsec): Countering fault attacks in modern microprocessors,” 2018 IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), Washington, DC, 2018, pp. 235-238.

doi: 10.1109/HST.2018.8383922

[5] https://www.cosic.esat.kuleuven.be/summer_school_sardinia_2015/slides/Balasch.pdf.

[6] Yuce et al. 2016. Software Fault Resistance is Futile: Effective Single-Glitch Attacks. In 2016 Workshop on Fault Diagnosis and Tolerance in Cryptography, FDTC 2016, Santa Barbara, CA, USA, August 16, 2016.47–58.

[7] GabbayandGabbay.1996. Speculative Execution based on Value Prediction.TechnicalReport.EEDepartmentTR1080,Technion-IsraelInstitueofTechnology.

[8] Perais and Seznec. 2014. Practical data value speculation for future high-end processors.In20th IEEE International Symposium on High-Performance Computer Architecture, HPCA 2014, Orlando, FL, USA, February 15-19, 2014.428–439.

[9] G.DiNataleetal.,“Areliablearchitectureforparallelimplementations oftheAdvancedEncryptionStandard,”J.Electron.Testing,vol.25,no. 4, pp. 269–278, 2009.

[10] M. Mozaffari-Kermani et al., “Fault-resilient lightweight cryptographic block ciphers for secure embedded systems,” IEEE Embed. Syst. Lett., vol. 6, no. 4, pp. 89–92, Dec. 2014.

[11] X. Guo and R. Karri, “Recomputing with permuted operands: A concurrenterrordetectionapproach, “IEEETrans.Comput.-AidedDesign Integr.CircuitsSyst.,vol.32,no.10,pp.1595–1608,Oct.2013.

[12] R.Karrietal., “Concurrenterrordetectionoffault-basedside-channel cryptanalysis of 128-bit symmetric block ciphers,” in Proc. DAC’01, pp. 579–585.

[13] OpenSSL,CryptographyandSSL/TLSToolkit. http://www.openssl.org

[14] StandardPerformanceEvaluationCorporation. TheSPECCPU2017Benchmark Suite. https://www.spec.org/cpu2017/

[15] StandardPerformanceEvaluationCorporation. TheSPECCPU2006Benchmark Suite. https://www.spec.org/cpu2006/

[16] SpMVBenchmark. http://bebop.cs.berkeley.edu/spmvbench/

Essay Writing Service Features

Our Experience

No matter how complex your assignment is, we can find the right professional for your specific task. Contact Essay is an essay writing company that hires only the smartest minds to help you with your projects. Our expertise allows us to provide students with high-quality academic writing, editing & proofreading services.

Free Features

Free revision policy

$10Free bibliography & reference

$8Free title page

$8Free formatting

$8How Our Essay Writing Service Works

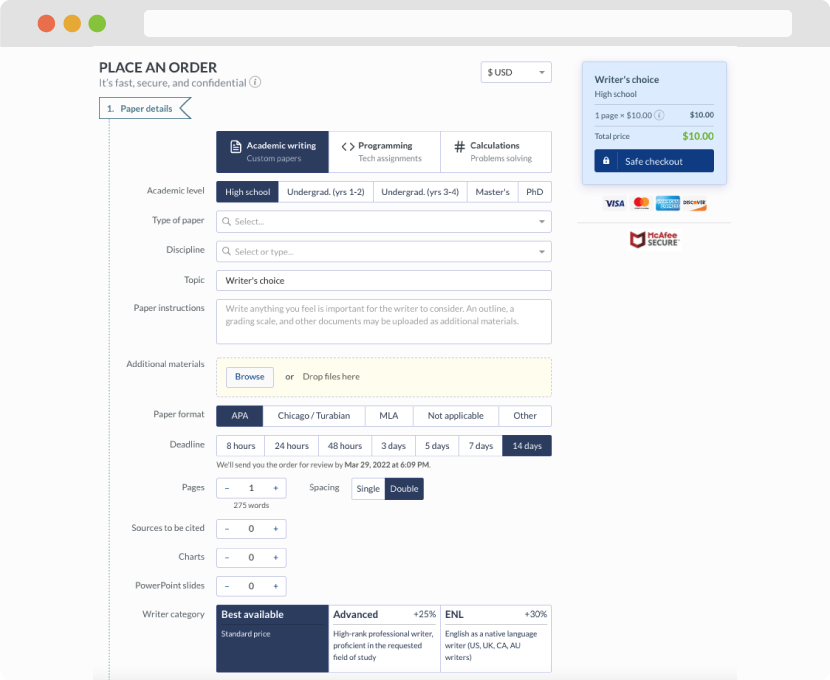

First, you will need to complete an order form. It's not difficult but, in case there is anything you find not to be clear, you may always call us so that we can guide you through it. On the order form, you will need to include some basic information concerning your order: subject, topic, number of pages, etc. We also encourage our clients to upload any relevant information or sources that will help.

Complete the order form

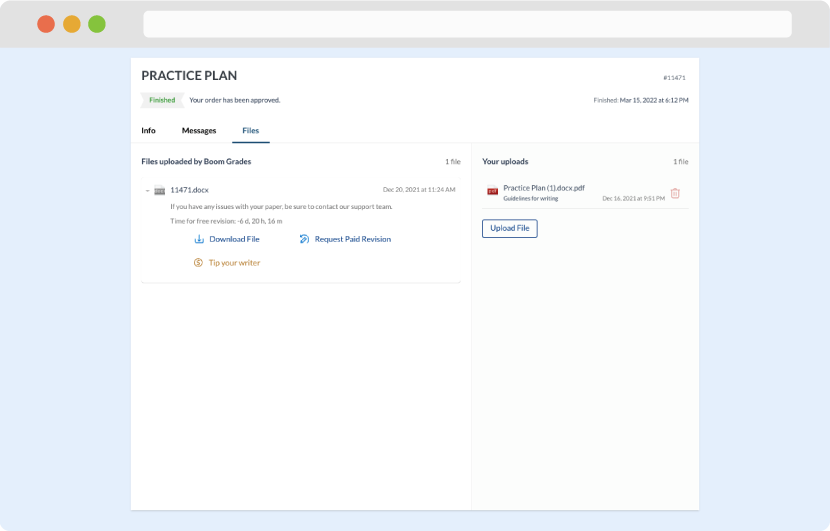

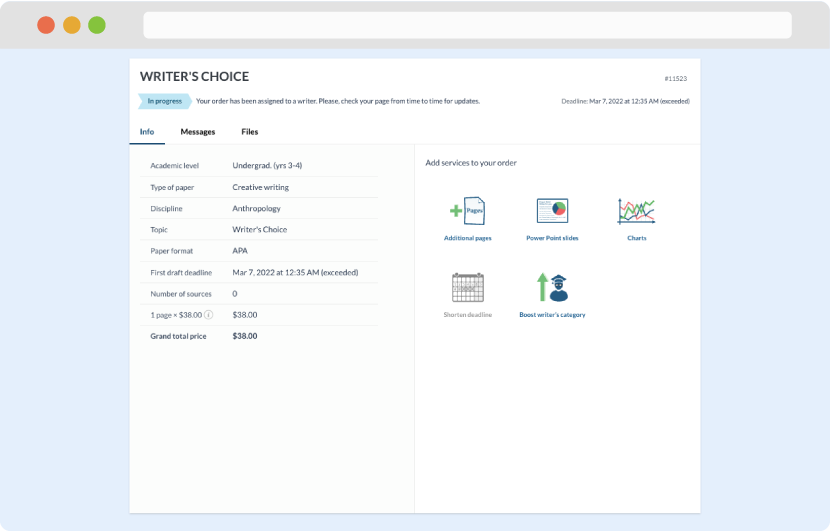

Once we have all the information and instructions that we need, we select the most suitable writer for your assignment. While everything seems to be clear, the writer, who has complete knowledge of the subject, may need clarification from you. It is at that point that you would receive a call or email from us.

Writer’s assignment

As soon as the writer has finished, it will be delivered both to the website and to your email address so that you will not miss it. If your deadline is close at hand, we will place a call to you to make sure that you receive the paper on time.

Completing the order and download