Table of Contents

List of Figures

List of Tables

Abstract

1.0 Introduction

2.0 Design Methodology

2.1Design of a 3-bit ALU using Proteus: A case study

2.2Basic components

2.2.1 Adder/Subtractor Block

2.2.2 Array Multiplier

2.2.3 Multiplexers

2.3 Design of a 4-bit ALU using Proteus

2.3.1 Operation table for a 4-bit ALU

2.3.2Adder/Subtractor block

2.3.3 4-Bit Comparator

APPENDICES

Figure 1: Basic Components of an Electronic Gates

Figure 2: Description of the shift and add algorithm

Figure 3: The Schematic diagram of a 4X1 Multiplexer

Figure 4: The Display page of a 3-Bit ALU

Figure 5: A typical Adder/Subtractor Circuit

Figure 6: Simulation of a full adder in proteus

Figure 7: Simulation of an adder/subtractor circuit in Proteus

Figure 8: Simulation of a 4-Bit Comparator in proteus

Table 1: The truth-table of a 4-bit ALU

Table 2: The truth-table of a full adder

Table 3: The Truth-table implementing a subtractor circuit

Table 4: The truth-table for a 4-bit comparator

Single Electron Transistor (SET) is a low-powered Nano device and as such it requires some sort of optimization at all levels to achieve a high-end performance. This paper will be presenting the design of a SET based 4-bit ALU using Proteus in view of its excellent potential for future Ultra Large Scale Integrated (ULSI) Circuits. The basic circuits required for this design such as Adder, multiplier and Comparator circuits will be designed & simulated using Proteus. However, the proposed logic design model is encouragingly operational at room temperature.

Get Help With Your Essay

If you need assistance with writing your essay, our professional essay writing service is here to help!

Essay Writing Service

Conversely, the SET-based ALU will be designed, simulated and optimized with incorporation of necessary and sufficient parameters in the feasible fabrication range in a hierarchical manner. It is expected that after simulation and design, we would be able to corroborate that a SET-based ALU is more efficient than CMOS-based ALU or its derivatives in terms of power consumption, delay and effectiveness. The analyses of the result could be performed if possible at 45nm technology node using Cadence EDA tool and of course, performance-based comparisons will be made with CMOS-based ALUs at percentages based on different parameters considered.

1.0 Introduction

The exponential increase in the density of integrated circuits predicted by Moore’s law has been mainly driven by reducing the dimensions of the semiconductor devices comprising these circuits. However, as semiconductor feature sizes shrink into the nanometer scale regime, device behavior becomes increasingly problematic as new physical phenomena at short dimensions occur, and limitations in material properties are reached. In effect, the SET technology circumvented the attendant problems common with CMOS technology which borders on speed and performance.

SETs are promising building blocks for future high-density and low-powered integrated circuits. In this paper, a SET-based 4-bit Arithmetic and Logic Unit (ALU) is discussed with necessary functionalities. Essentially, paper formulation is as follows: Section 2 talks about the design and simulation of a 4-bit ALU in details. Section 3 provides simulation results and section 4 is conclusion.

1.1 Single Electron Transistors (SETs)

A single-electron transistor (SET) is a sensitive electronic device based on the Coulomb blockade effect. In this device the electron flows through a tunnel junction between source/drain to a quantum dot (conductive island). Moreover, the electrical potential of the island can be tuned by a third electrode, known as the gate, which is capacitively coupled to the island. Figure 1 Below shows the basic schematic of a SET device. The conductive island is sandwiched between two tunnel junctions,[1] which are modeled by a capacitance (CD and CS) and a resistor (RD and RS) in parallel. (Source: Wikipedia).

Figure 1: The Basic Schematic of a SET device

The SET operates mainly as a switch and the fact that SETs may exhibit negative trans-conductance which allows the implementation of complementary circuits using transistors of a single type.

2.1Design of a 3-bit ALU using Proteus: A case study

An ALU is a combinational logic circuit, meaning that its outputs will change asynchronously in response to input changes.

2.2Basic components

As a case study, I designed a 3-bit ALU to be able to explain a more complex 4-bit ALU. Basically, an ALU is made up of: an arithmetic and logic units. However, the basic components used to develop this sub units are electronic gates such as AND gate, OR gate, XOR gate, XNOR gate and the NOT gate. The truth table and circuit symbol of the aforementioned gates are shown below:

Figure 2: Basic Components of an Electronic Gates

More importantly, a typical ALU has sub circuitry in the child sheet of the design. It include the Addition/Subtractor, Array Multiplier, multiplexer and Logic unit blocks. This paper briefly explain all the sub-block in the child’s sheet of the design.

2.2.1 Adder/Subtractor Block

In digital circuits, an adder-Subtractor block is a circuit that is capable of adding or subtracting numbers in a binary system under the influence of a control signal (either 0 or 1).

2.2.2 Array Multiplier

Array multiplier is well known due to its regular structure. Multiplier circuit is based on add and shift algorithm. Each partial product is generated by the multiplication of the multiplicand with one multiplier bit. The partial product are shifted according to their bit orders and then added.

Figure 3: Description of the shift and add algorithm

2.2.3 Multiplexers

Multiplexer is a combinational circuit that has maximum of 2n data inputs, ‘n’ selection lines and single output line. One of these data inputs will be connected to the output based on the values of selection lines. Since there are ‘n’ selection lines, there will be 2n possible combinations of zeros and ones. So, each combination will select only one data input. Multiplexer is also called as Mux.

Figure 4: The Schematic diagram of a 4X1 Multiplexer

One of these 4 inputs will be connected to the output based on the combination of inputs present at these two selection lines. Truth table of 4×1 Multiplexer is shown below.

Selection Lines

Output

S0

S1

Y

0

0

I0

0

1

I1

1

0

I2

1

1

I3

From Truth table, we can directly write the Boolean function for output, Y as:

Y= I0 S0̅ S1̅+ I1S0̅ S1+ I2S0S1̅+ I3S0S1

The design interface of a 3-bit ALU is shown below which is able to perform addition, subtraction, multiplication and shifting operation. The picture below is just the parent sheet of the design. In the appendices section, this paper will show the full circuit.

Figure 5: The Display page of a 3-Bit ALU

2.3 Design of a 4-bit ALU using Proteus

Arithmetic and Logic Unit (ALU) is made of Arithmetic and Logic Units. This paper considers and designed sub-blocks such as Adder/subtraction block, 4-bit multiplier, Magnitude Comparator and Multiplexers using Proteus.

2.3.1 Operation table for a 4-bit ALU

Table 1: The truth-table of a 4-bit ALU

Inputs

S2

S1

S0

Cin

Function

Output

Width

0

0

0

0

Addition

5-bit

0

0

0

1

Subtraction

4-bit

0

0

1

0

Multiplier

8-bit

0

0

1

1

Magnitude Comparator

3-bit

0

1

0

0

Logical Left Shifter

4-bit

0

1

0

1

Logical Right Shifter

4-bit

0

1

1

0

Right Rotator

4-bit

0

1

1`

1

Left Rotator

4-bit

1

0

0

0

Bitwise Inversion

4-bit

1

0

0

1

Bitwise AND

4-bit

1

0

1

0

Bitwise OR

4-bit

1

0

1

1

Bitwise XOR

4-bit

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

2.3.2Adder/Subtractor block

The logical gates discussed so far can be used for performing arithmetical functions like addition,

Subtraction, multiplication and division in electronic calculators and digital instruments. In the

Central processing unit (CPU) of a computer, these arithmetic functions are carried out by the

Arithmetic and Logic Unit (ALU). The logic functions used generally are AND, XOR and OR gates. A typical adder/ Subtractor which is implemented using logic gates is shown below.

Figure 6: A typical Adder/Subtractor Circuit

2.3.2.1 Full Adder

A full adder has three inputs and two outputs.It can add 3 digits (or bits) at a time. The bits A and B which are to be added come from the two registers and the third input comes from the carry generated by the previous addition. It produces two outputs; Sum and Carry-out. The truth table is shown below:

Table 2: The truth-table of a full adder

Input

Output

A

B

Cin

Sum

Carry-out

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

The resulting Boolean expression:

Sum, S= (A θ ̅B) θ ̅Cin and Carry–out = (A∙B)+ (Cin ∙ (A θ ̅B))

. The logic diagram of a FULL Adder is shown below.

Figure 7: Simulation of a full adder in proteus

2.3.2.2 Subtractor

This paper implements a subtractor circuit using the 2’s complement. For instance;

Table 3: The Truth-table implementing a subtractor circuit

A

B

Output (Y)

0

0

0

0

1

1

1

0

1

1

1

0

When

A = 0, Y=B

and when

A=1, Y= B̅

. Therefore, the Adder/Subtractor circuit is shown below:

Figure 8: Simulation of an adder/subtractor circuit in Proteus

2.3.3 4-Bit Comparator

Table 4: The truth-table for a 4-bit comparator

A2

A1

B2

B1

A>B

A=B

A<B

0

0

0

0

0

1

0

0

0

0

1

0

0

1

0

0

1

0

0

0

1

0

0

1

1

0

0

1

0

1

0

0

1

0

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

0

1

1

1

0

0

1

1

0

0

0

1

0

0

1

0

0

1

1

0

0

1

0

1

0

0

1

0

1

0

1

1

0

0

1

1

1

0

0

1

0

0

1

1

0

1

1

0

0

1

1

1

0

1

0

0

1

1

1

1

0

1

0

Equality Relationship ( A=B)

X1=1 if Ai= Bi for i=0, 1, 2, 3

∴If A3= B3 and A2= B2 and A1= B1 and A0= B0 . Then, X3=X2= X1= X0=1

. In essence, the equality Condition is satisfied when EQ = 1.

Greater than relationship (if

A >B)

This condition exist:

If A3> B3 → A3 =1 and B3=0

OR

If A3= B3 and A2> B2 → A2 =1 and B2=0 OR If A3= B3, A2= B2 and A1> B1 → A1=1 and B1= 0 OR If A3= B3, A2= B2 , and A1= B1, A0> B0 → A0=1 and B0= 0

Greater Than (GT) =

A3B3̅+ X3A2B2̅+X3X2A1B1̅+ X3X2X1A0B0̅

Less than Relationship (LT=1 if A<B)

This condition exist:

If A3< B3 → A3 =0 and B3=1

OR

If A3= B3 and A2=B2 → A2 =0 and B2=1 OR If A3= B3, A2= B2 and A1< B1 → A1=0 and B1= 1 OR If A3= B3, A2= B2 , and A1= B1, A0< B0 → A0=0 and B0= 1

Less Than (LT) =

A3̅B3+ X3A2̅B2+X3X2A1̅B1+ X3X2X1A0̅B0

Using Karnaugh map to simplify the greater than, less than and equal to relationship.

For A>B

y1= A2̅A1B2̅ B1̅+ A2A1̅ B2̅ B1̅+ A2A1̅ B2̅ B1+ A2A1 B2̅ B1̅+ A2A1 B2̅ B1+ A2A1 B2 B1̅

y1= B2̅A2+ B1̅A2A1+ B2̅ B1̅A1

For A= B

y2=A2 θ̅ B2* A1 θ̅ B1

For A< B

y3= B2A2̅+ B1A2̅ A1̅+ B2B1A1̅

The equivalent representation of a 4-bit comparator in proteus is shown below:

Figure 9: Simulation of a 4-Bit Comparator in proteus

References

Horea Gozar¹, Alexandru Chira², Örs Nagy³, Zoltán Derzsi. (2018, Jan 29). Medical Use of Finite Element Modeling of the Ankle and Foot. Journal of Inter-disciplinary Medicine.

Qin Li, Li Cai, Youjie Zhou, Gang Wu and Sen Wang. (2008). Design and Simulation of Logic Circuits by Combined Single-Electron/MOS Transistor Structures. IEEE Conference on Nano/Micro Engineered and Molecular Systems (pp. 6-9). China: IEEE. Retrieved October 4, 2018

Rathin Joshi, Yash Agrawal, Rutu Parekh. (2017). Design and Optimization of Single Electron Transistor base 4-Bit Arithmetic and Logic Unit at Room Temperature Operation. IEEEE International Symposium on Nanoelectronic and Information Systems (pp. 34-39). India: IEEE Computer Society. Retrieved October 10, 2018

Vaishali Rant, P.K. Dakhole. (2015). Design and Implementation of four bit Arithmetic and Logic Unit using hybrid Single Electron Transistor and Mosfet at 120nm Technology. International Conference on Pervasive Computing (ICPC). India. Retrieved October 1, 2018

Vaishali Raut, P. D. (2014). Design and Implementation of Single Electron Transistor N-Bit Multiplier. International Conference on Circuit, Power and Computing Technologies (ICCPCT) (pp. 1099-1104). India: IEEE. Retrieved October 8, 2018

Yongshun Sun, Rusli, and Navab Singh. (2011). Room-Temperature Operation of Silicon Single Electron Transistor Fabricated using Optical Lithography. IEEE Transactions on Nanotechnology, 10. Retrieved october 9, 2018

Essay Writing Service Features

Our Experience

No matter how complex your assignment is, we can find the right professional for your specific task. Contact Essay is an essay writing company that hires only the smartest minds to help you with your projects. Our expertise allows us to provide students with high-quality academic writing, editing & proofreading services.

Free Features

Free revision policy

$10Free bibliography & reference

$8Free title page

$8Free formatting

$8How Our Essay Writing Service Works

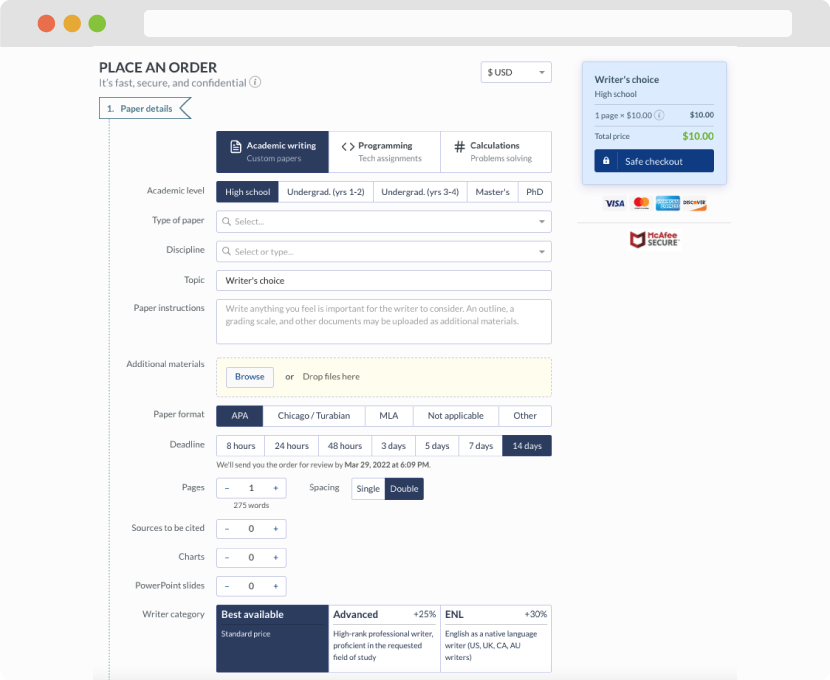

First, you will need to complete an order form. It's not difficult but, in case there is anything you find not to be clear, you may always call us so that we can guide you through it. On the order form, you will need to include some basic information concerning your order: subject, topic, number of pages, etc. We also encourage our clients to upload any relevant information or sources that will help.

Complete the order form

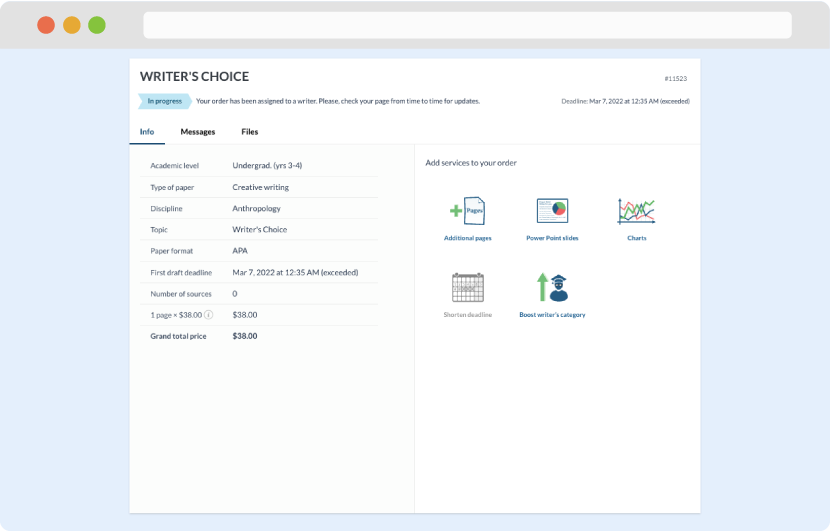

Once we have all the information and instructions that we need, we select the most suitable writer for your assignment. While everything seems to be clear, the writer, who has complete knowledge of the subject, may need clarification from you. It is at that point that you would receive a call or email from us.

Writer’s assignment

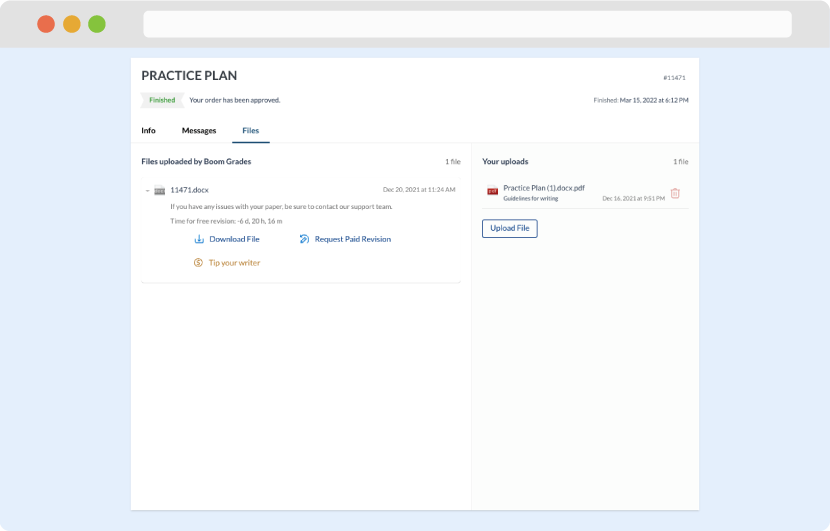

As soon as the writer has finished, it will be delivered both to the website and to your email address so that you will not miss it. If your deadline is close at hand, we will place a call to you to make sure that you receive the paper on time.

Completing the order and download