A High Swinging Ultra-Low-Power Two Stage CMOS OP-AMP in 0.18 um Technology with 1.2v supply, is presented. Cascode technique has been used to increase the dc addition. The unity-gain bandwidth is besides enhanced utilizing a gain-stage in the Miller capacitance feedback way. The proposed opamp provides 236MHz unity-gain bandwidth, 109.7 degree stage border. The circuit has 94.34dB addition. The power dissipation of the designed merely is about 50uw. The intentional system demonstrates comparatively suited response in different temperature.

( 1 ) Introduction: -Operational Amplii¬?ers ( Op As ) are one of the most widely used edifice blocks for parallel and mixed-signal systems.

They are employed from District of Columbia prejudice applications to high velocity amplii¬?ers and i¬?lters. General purpose op As can be used as bui¬ˆers, summers, planimeters, dii¬ˆerentiators, comparators, negative electric resistance convertors, and many other applications. With the speedy betterments of computing machine aided design ( CAD ) tools, promotions of semiconducting material mold, steady miniaturisation of transistor grading, and the advancement of fiction procedures, the incorporate circuit market is turning quickly.

Nowadays, complementary metal-oxide semiconducting material ( CMOS ) engineering has become dominant over bipolar engineering for parallel circuit design in a mixed-signal system due to the industry tendency of using standard procedure engineerings to implement both parallel circuits and digital circuits on the same bit. While many digital circuits can be adapted to a smaller device degree with a smaller power supply, most bing parallel circuitry requires considerable alteration or even a redesign to carry through the same effort. With transistor length being scaled down to a few 10s of nanometres, parallel circuits are going progressively more dii¬?cult to better upon.

The operational amplifier is one of the most utile and of import constituents of parallel electronics. They are widely used in popular electronics. Their primary restriction is that they are non particularly fast: The typical public presentation degrades quickly for frequences greater than approximately 1 MHz, although some theoretical accounts are designed specifically to manage higher frequences.

The primary usage of op-amps in amplifier and related circuits is closely connected to the

Concept of negative feedback. Feedback represents a huge and interesting subject in itself. We will discourse it in fundamental footings a spot subsequently. However, it is possible to acquire a feeling for the two primary types of amplifier circuits, inverting and non-inverting, by merely contending a few simple regulations ( the golden regulations ” ) . We will get down in this manner, and so travel back to understand their beginning in footings of feedback.

( 2 ) Basic Block diagram CMOS op-amp: – Operational Amplifiers are the anchor for many parallel circuit designs. Op-Amps are one of the basic and of import circuits which have a broad application in several parallel circuits such as switched capacitance filters, algorithmic, pipelined and sigma delta A/D convertor, sample and keep amplifier etc. The velocity and truth of these circuits depends on the bandwidth and DC addition of the Op-amp. Larger the bandwidth and addition, higher the velocity and truth of the amplifier Op-amp are a critical component in parallel sampled informations circuit, such as SC filters, modulators. The general block diagram of an op-amp with an end product buffer is shown below

hypertext transfer protocol: //s.eeweb.com/members/jessica_shoemaker/projects/2011/03/22/Image1-1300812338.png

Figure 1. Block diagram of Op-Amp

The first block is a differential amplifier. It has two inputs which are the inverting and non-inverting electromotive force. It provides at the end product a differential electromotive force or a differential current that, basically, depends on the derived function input merely. The following block is a differential to single-ended convertor. It is used to transform the differential signal generated by the first block into a individual ended version. Some architecture does n’t necessitate the derived function to individual ended map ; therefore the block can be excluded. In most instances the addition provided by the input phases is non sufficient and extra elaboration is required. This is provided by intermediate phase, which is another differential amplifier, driven by the end product of the first phase. As this phase uses differential input unbalanced end product derived function amplifier, so it provide required excess addition. The prejudice circuit is provided to set up the proper operating point for each transistor in its impregnation part. Finally, we have the end product buffer phase. It provides the low end product electric resistance and larger end product current needed to drive the burden of op-amp or improves the slew rate of the op -amp. Even the end product phase can be dropped: many incorporate applications do non necessitate low end product electric resistance ; moreover, the batch rate permitted by the addition phase can be sufficient for the application. If the op-amp is intended to drive a little strictly capacitive burden, which is the instance in many switched capacitance or informations transition applications, the end product buffer is non used. When the end product phase is non used the circuit, it is an operational transconductance amplifier, OTA. The intent of the compensation circuit is lower the addition at high frequences and to keep stableness when negative feedback is applied to the op A.

A. Circuit Operation The concluding circuit designed to run into the needed specifications is shown in Figure 2. The topology of this circuit is that of a standard CMOS op-amp. It comprised of three subdivisions of

hypertext transfer protocol: //www.silvaco.com/tech_lib_TCAD/simulationstandard/1995/mar/a2/a2_fig1.gif

Figure2. The topology chosen for this Op-Amp design.

Circuit, viz. differential addition phase, 2nd addition phase and bias strings. It was found that this topology was able to successfully run into all of the design specifications.

Transistors M1, M2, M3, and M4 form the first phase of the op amp the differential amplifier with differential to individual ended transmutation. Transistors M1 and M2 are standard N channel MOSFET ( NMOS ) transistors which form the basic input phase of the amplifier. The gate of M1 is the inverting input and the gate of M2 is the non-inverting input. A differential input signal applied across the two input terminuss will be amplified harmonizing to the addition of the differential phase. The addition of the phase is merely the transconductance of M2 times the entire end product opposition seen at the drain of M2. The two chief oppositions that contribute to the end product opposition are that of the input transistors themselves and besides the end product opposition of the active burden transistors, M3 and M4. The current mirror active burden used in this circuit has three distinguishable advantages. First, the usage of active burden devices creates a big end product opposition in a comparatively little sum of die country. The current mirror topology performs the differential to single-ended transition of the input signal, and eventually, the burden besides helps with common manner rejection ratio. In this phase, the transition from differential to individual ended is achieved by utilizing a current mirror ( M3 and M4 ) . The current from M1 is mirrored by M3 and M4 and subtracted from the current from M2. The differential current from M1 and M2 multiplied by the end product opposition of the first phase gives the single-ended end product electromotive force, which constitutes the input of the 2nd addition phase.

C. Second Gain Stage The 2nd phase is a current sink burden inverter. The intent of the 2nd addition phase, as the name implies, is to supply extra addition in the amplifier. Consisting of transistors M5 and M6, this phase takes the end product from the drain of M2 and amplifies it through M5 which is in the standard common beginning constellation. Again, similar to the differential addition phase, this phase employs an active device, M6, to function as the burden opposition for M5. The addition of this phase is the transconductance of M5 times the effectual burden opposition comprised of the end product oppositions of M5 and M6. M6 is the driver while M7 acts as the burden.

The design in this undertaking is a two-stage op A with an n-channel input brace. The op A uses a dual-polarity power supply ( Vdd and Vss ) so the Ac signals can swing above and below land and besides be centered at land. The manus computation consequences provided the estimated parametric quantities ( such as transistor breadth and length, electrical capacity, etc. ) to do the circuit conventional ( shown in figure ) in Design Architect IC and for the circuit analysis in Model Sim Eldo of Mentor Graphic Tool.Schematic used in this design is

Degree centigrades: Documents and SettingsstudentDesktop44132421.png

Design of two phase opamp utilizing wise man artworks

Using Mentor Graphics EDA Tool we have design High Swinging Ultra-Low-Power Two Stage CMOS OP-AMP as shown in conventional window. Fig 1 & A ; Fig 2 shows the Gain and Phase secret plan for basic two phase opamp. After simulation we have analyzed that the addition of the opamp is 94.34db and have a stage border of 109.7 grade at 40 MHz frequence. This analysis can be made possible utilizing different size of the MOS transistor at different phases. There graphs are as

Degree centigrades: UsersDellDesktopopampGAIN GRAPH.png

Fig. 1 Gain graph

Degree centigrades: UsersDellDesktopopampPM.png

Fig.2 stage border secret plan

From the mention paper [ 14 ] we have seen that the addition is 90 dubnium which is improves up to 94.3db which is used in any of Analog planing.

Table shows the brief of consequences as

PROCESS TECHNOLOGY

180nm

Addition

94.34 dubnium

PHASE MARGIN

109.7° at 40MHZ

Essay Writing Service Features

Our Experience

No matter how complex your assignment is, we can find the right professional for your specific task. Contact Essay is an essay writing company that hires only the smartest minds to help you with your projects. Our expertise allows us to provide students with high-quality academic writing, editing & proofreading services.

Free Features

Free revision policy

$10Free bibliography & reference

$8Free title page

$8Free formatting

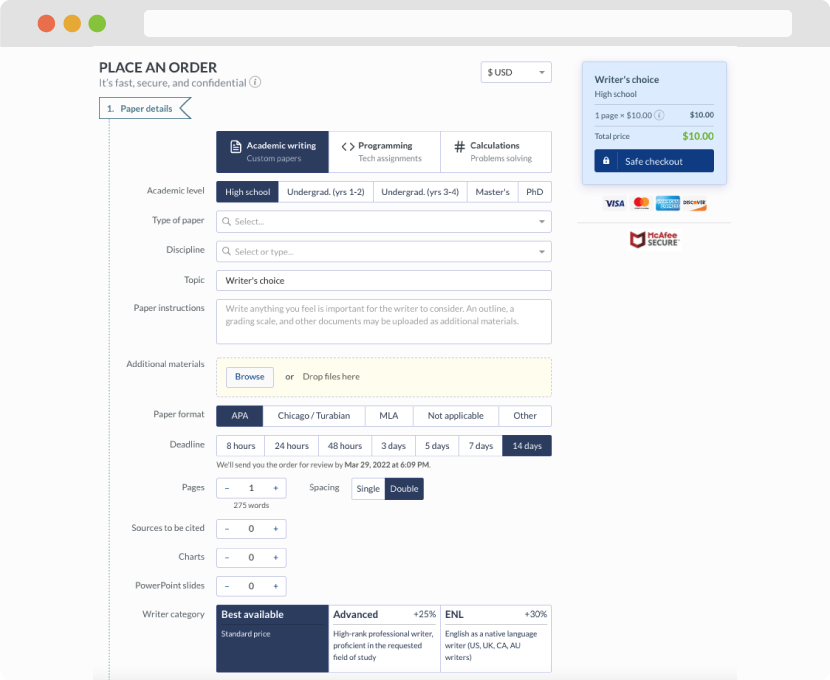

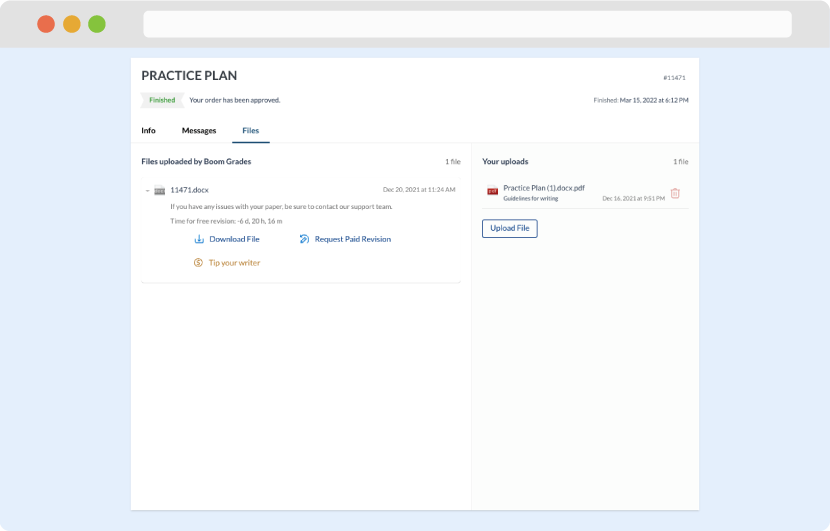

$8How Our Essay Writing Service Works

First, you will need to complete an order form. It's not difficult but, in case there is anything you find not to be clear, you may always call us so that we can guide you through it. On the order form, you will need to include some basic information concerning your order: subject, topic, number of pages, etc. We also encourage our clients to upload any relevant information or sources that will help.

Complete the order form

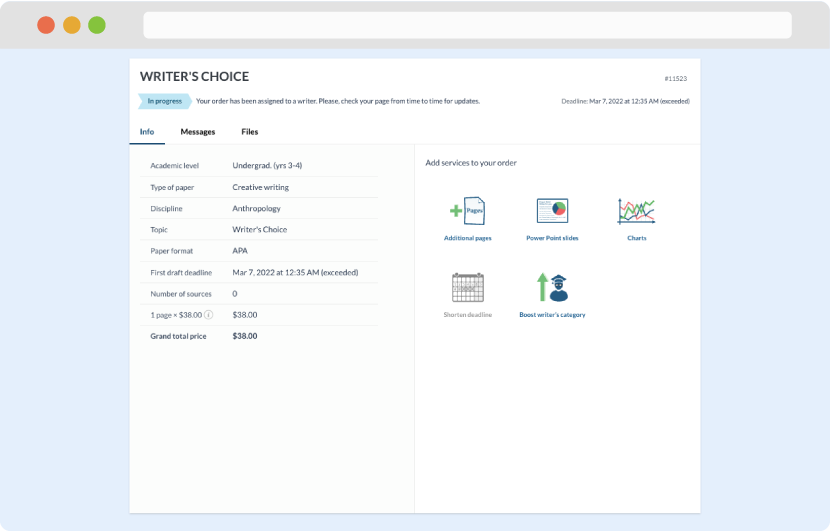

Once we have all the information and instructions that we need, we select the most suitable writer for your assignment. While everything seems to be clear, the writer, who has complete knowledge of the subject, may need clarification from you. It is at that point that you would receive a call or email from us.

Writer’s assignment

As soon as the writer has finished, it will be delivered both to the website and to your email address so that you will not miss it. If your deadline is close at hand, we will place a call to you to make sure that you receive the paper on time.

Completing the order and download