Reed-Solomon is an error-correcting codification capable of covering with rectifying multiple mistakes, specifically burst mistakes. It is signifier of particular non binary subclass of BCH ( Bose, Chaudhari and Hocqueng ) codes. It can rectify up to ( n-k ) /2 or T symbols. Programmable-hardware devices are the best pick for Reed-Solomon codec execution, because these devices contain an copiousness of the registries that the hardware-implementation procedure requires. Easily function of equations is possible on the LUT architecture of FPGAs.

Reed-Solomon mistake rectifying codifications ( RS codifications ) are widely used in communicating systems and informations storages to retrieve informations from possible mistakes that occur during transmittal and from disc mistake severally [ 3 ] .

One typical application of the RS codifications is the Forward Error Correction ( FEC ) [ 1 ] .

Before informations transmittal, the encoder attaches para symbols to the informations utilizing a preset algorithm before transmittal. At the having side, the decipherer detects and corrects a limited preset figure of mistakes occurred during transmittal. Conveying the excess para symbols requires excess bandwidth compared to conveying the pure informations.

However, conveying extra symbols introduced by FEC is better than retransmitting the whole bundle when at least an mistake has been detected by the receiving system.

For a typical channel, the add-on of RS coding allows the system to run within about 4 dubnium of the Shannon capacity. The resulting benefit translates into higher information rates, lower bit-error rates ( BERs ) , greater transmittal distance, and greater unsusceptibility to interference effects [ 2 ] .

RS codecs can be implemented in a figure of platforms, traditionally being Application Specific Integrated Circuits ( ASICs ) , and so switching towards DSP and Programmable Logic Devices ( PLDs ) [ 3 ] . FPGAs provide the advantage of easy design reuse, faster design clip particularly for prototyping [ 4 ] . A choice of the most suited FEC to be used with the system may be provided utilizing the benefit of reprogrammability of FPGAs. In fact, programmable-hardware devices are most recommended for Reed-Solomon-codec execution due to the copiousness of registries that the hardware execution requires. Parallel realisation of equations is possible to run into clip velocity restraints. Equations with multipliers and power/ inversion circuits may be mapped into the look-up tabular array ( LUT ) architecture of FPGAs. The RAMs available farther cut down hardware resources [ 5 ] .

A Reed-Solomon codification is a block codification and can be specified as RS ( n, K ) as shown in Fig. 1. The variable N is the size of the codeword with the unit of symbols, K is the figure of informations symbols and 2t is the figure of para symbols each symbol contains s figure of spots.

PARATY

Datas

K 2t

N

Fig.1 The construction of a RS codeword

For a symbol size s, the maximal codeword length ( n ) for a Reed-Solomon codification is

n = 2s – 1

The RS codification allows to rectify up to t figure of symbol mistakes where T is given by

T = n – K

2

A popular Reed-Solomon codification is RS ( 255,223 ) with 8-bit symbols. Each codeword contains 255 codification word bytes, of which 223 bytes are informations and 32 bytes are para. For this codification:

n = 255, k = 223, s = 8

2t = 32, T = 16

A. Galois Field

RS codifications are based on finite Fieldss, called Galois Fieldss. Rather so look at single Numberss and equations, the attack of modern mathematicians is to look at all the Numberss that can be obtained from some given initial aggregation by utilizing operators such as add-on, minus, generation and division. The ensuing aggregation is called a field. Every component, except zero, can be expressed as a power of a crude component, I± , of the field. The non-zero field elements form a cyclic group defined based on a binary crude multinomial. Some Fieldss, like the set of whole numbers, are infinite. This causes jobs when they represent on a computing machine with a fixed length word. Galois field have the utile belongings that any operation on an component of the field will ever ensue in another component of the field. Field component values are shown in Table 1.

B. Arithmatic Operation

I. Addition

Addition is defined as the bitwise sole or of two Numberss in a field.

i.e 6+2=4, 1+2=3

1+3=2, 3+6=5

A definition of add-on agencies that subtraction gives the same consequence as add-on. This can be seen by the fact that adding any to Numberss in the field ( utilizing the bitwise XOR add-on ) , will give a consequence of 0, as all 1 spots will be changed to 0, and the 0 ‘s will stay unchanged.

Therefore a figure is its ain linear opposite. Therefore all minus operations can be replaced by add-on operations.

Exponential

Form

Polynomial

Form

Index

Forms

( Spots )

Index Form

( Value )

0

0

0 0 0

0

1=I±0

1

0 0 1

1

I±1

ten

0 1 0

2

I±2

x2

1 0 0

4

I±3

x3=1+x

0 1 1

3

I±4

x4=x.x3

=x+x2

1 1 0

6

I±5

x5=x2+x3

=x2+x+1

1 1 1

7

I±6

x6=x3+x2+x

=x2+1

1 0 1

5

I±7

x7=x3+x

=x+x+1

=1

0 0 1

1

Table 1 Field component value assignments utilizing multinomial representation

two. Generation

Generation is defined as value that is obtained when the advocates of I± , are added and converted back into index signifier.

Multiples of I±n can be removed from the generation look, as these represent 1, which has generation individuality, and therefore has no consequence. Using the Galois field some illustrations are as follows:

1*x = I±0*I±y = I±y = x ( where ten is field component )

2*3 = I±1*I±3 = I±4 = 6

3*7 = I±3*I±5 = I±8 = I±1*I±7 =I±1*1 =I±1 = 2

three. Differentiation

Let any vth grade multinomial given by:

U ( x ) = UvXv + Uv-1Xv-1 + aˆ¦+ U2X2 + U1X + U0

Then we can specify U ‘ ( ten ) as:

U ‘ ( ten ) = vUvXv-1 + ( v-1 ) Uv-1Xv-2 + aˆ¦aˆ¦aˆ¦+ U5X4 + U3X2 + U1

Where jUj =0 when J is even and jUj=Uj when J is uneven, for illustration

For U ( x ) = vX4 + v2X3 + vX2 + X + v5 so

U ‘ ( ten ) = v2X2+1.

C. Codeword

Reed-Solomon codifications are signifier of additive cyclic multinomial codifications. This means that the elements used in Reed-Solomon codifications can be represented by multinomials, coefficients of which are members of a Galois field ( GF ( 2M ) .

The end product of the encoding procedure consequence in codification words, which is the information with para bytes added to the information. The notation of Reed-Solomon codifications indicates that the length of the information multinomial is thousand bytes, while the figure of para bytes that are added is 2t. The length of the codeword ( information and para bytes ) is n.

N is given by the expression: n=2M-1

N is besides represented by: n=k+2t

D. Generator Polynomial

Mistake rectifying codifications require a systematic method of finding the para spots which should be added, given a peculiar watercourse of information. To enable this systematic method of finding the para bytes, a generator multinomial is required. This generator multinomial is used in the encryption and decrypting procedure.

The generator multinomial is given by:

2t-1

g ( X ) = ?Y ( X + I±i )

i=0

Where I± is the crude component.

g ( x ) = ( x+I±0 ) ( x+I±1 ) ( x+I±2 ) aˆ¦ . ( x+I±2t-2 ) ( x+I±2t-1 )

g ( x ) =x2t + g2t-1x2t-1 + aˆ¦.. +g3x3 + g2x2 + g1x +g0

the coefficients g0, aˆ¦.g2t-1 are elements of GF.

The codification words c ( x ) of the Reed-Solomon codification are determined by utilizing the undermentioned expression:

degree Celsius ( x ) =i ( x ) .g ( x )

Fig. 2 Architecture of RS encoder

Where g ( x ) is the generator multinomial,

I ( ten ) is the information ( information ) multinomial.

A faster manner of encoding information is to obtain the 2t para symbols is to utilize the alternate encryption expression:

P ( x ) =i ( x ) . xn-k mod g ( ten )

Where P ( x ) is the para multinomial holding length of 2t.

P ( x ) is calculated modulo to the generator multinomial g ( x ) . This computation is tantamount to obtaining the balance when the information is shifted by 2t topographic points, and being divided by the generator multinomial. Each byte of informations is fed into the displacement registries, foremost being multiplied by the coefficients of the generator multinomial. It is so added to the component of the displacement registry from the old informations component, and set in the storage registry. These storage registries are all initialized to 0 at the start of the encoding algorithm.

The high degree architecture of the decrypting informations way is shown in Fig.3. Decoding RS codifications involves the extraction of two information entities from the received word. These are the set of Partial Syndromes, and the Error Locator Polynomial. From these two parametric quantities, Error Locations and Error magnitudes are extracted, and are straight applied upon the standard word to pull out the original, corrected message.The decipherer foremost calculates the syndrome of the receiving codeword to observe any possible mistakes occurred during transmittal. If the syndrome multinomial, S ( x ) , is non zero, the receiving codeword is hence erroneous and will be corrected if the figure of erroneous symbols is less than eight.

Fig. 3 Block Diagram of RS Decoder

I. Syndrome Calculation

The standard multinomial is denoted by R ( x ) , which is the information sent ( degree Celsius ( x ) ) with some noise added N ( x ) .

i.e. : R ( x ) = degree Celsius ( x ) + n ( ten ) .

I±i

reg

Received informations

Syndrome Si

Fig. 4 Architecture of syndrome reckoner

Syndrome computation can be done by an iterative procedure, such that the reply ( 2t syndrome symbols ) is available every bit shortly as the last para symbol has been read in. The syndromes represent information about the noise, independent of the informations that was sent.

two. Error Polynomial

The 2nd measure is to happen the mistake multinomial lambda. This requires work outing 2t coincident equations, one for each syndrome. The 2t syndromes form a coincident equation with t terra incognitas. The terra incognitas are the locations of the mistakes. The Error Locator Polynomial is a multinomial whose roots straight defined the mistake locations in the standard word. Berlekamp-Massey Algorithm is used to happen out mistake locater multinomial. The Berlekamp-Massey algorithm is a shift-register synthesis algorithm. It takes as input the n-k partial syndromes and outputs the mistake locater multinomial.

three. Error Location

After the Error Locator Polynomial has been computed, the roots of this multinomial have to be calculated in order to cognize the mistake locations. This is done by executing the Chien Search, which evaluates the Error Locator Polynomial at all elements of the GF ( 2m ) .The chien ‘s algorithm calculates the location of the erroneous symbols in each codeword. It evaluate the multinomial I› ( ten ) at all the field elements of GF ( 2m ) for a given Reed-Solomon ( n, K ) codification.

four. Error Magnitude

To measure the magnitude of the mistakes at the peculiar mistake locations, the mistake magnitude multinomial denoted by I© ( x ) needs to be determined. This multinomial is defined as,

I© ( x ) = S ( x ) I› ( x ) mod X2t

The Forney algorithm is used to calculate for the mistake magnitudes Wij, matching to the several mistake locations. Wij can be found out utilizing the undermentioned equation:

Wij = -Xj I© ( Xj-1 )

I› ‘ ( Xj-1 )

Where, Xj is the mistake location ( in the index signifier ) . Xj-1 is the opposite of the mistake location. I› ‘ ( ten ) is the derived function of the mistake locater multinomial.

v. Error Corrector

The mistake corrector block takes the standard codification and merely adds with the corresponding mistake magnitude that computes at the several mistake location to achieve the original message watercourse.

1. Advantages

I. Burst mistake correcting codification

A well-known illustration of a Reed-Solomon codification is RS ( 255, 223 ) with 8-bit symbols. For this specific Reed-Solomon codification, each codification word has 255 sum bytes, with 223 bytes of informations and 32 bytes for para. So the decipherer can automatically rectify 16 symbol mistakes anyplace in the codification word.

two. Power Savings Resulting from “ Coding Addition ”

It allows for transmittal at lower power degrees. This power economy is called “ coding addition, ” and it allows permutation of lower-cost, lower-power parts in sender electronics.

2. Disadvantages

Optical communicating requires really fast mistake rectifying decipherers at lower signal to resound ratio. So we ca n’t utilize RS Codes with Optical communicating because of its relatively slower decryption technique. Performance of Product codification is better than RS ( 255,223 ) in Optical communicating at lower SNR.

i. Encoder end product

Fig. 5 Encoder end product wave form

two. Decoder end product

Fig. 6 Decoder end product wavform

Use of error-control codifications reduces intervention effects, and FECs in general, extinguish the demand for retransmission of informations watercourses. The theoretical public presentation of Reed-Solomon codifications in bursty noise channels makes it a really good pick for FEC. With the handiness of LUTs, RAMs and registries, FPGAs have become a suited solution to RS executions.

Richard E. Balahut, “ Theory and Practice of Error Control Codes ” , Addison-Wesely Pub, 1983.

Richard E. Balahut, “ Algebric Codes for Data Transmission ” , Cambridge Publisher, 2003

S. B. Wicker, V. Bhargava, “ Reed Solomon Codes and their Applications ” , IEEE Press, 1994.

W.J. Ebel, W. H. Tranter, The Performance of Reed-Solomon Codes on a Bursty-Noise Channel, IEEE Transactions on Communications, Vol. 43, No. 2/3/4, February/March/April 1995

S. S. Shah, “ Self-correcting ocodes counquer noise ” , Part II: Reed-Solomon codecs, Design Feature, Electronic Design News, March 2001.

H. Chang, C. Shung, C. Li, “ A Reed-Solomon Product-Code ( RS-PC ) Decoder Chip for DVD Applications ” , IEEE Journal of Solid-State Circuits, Vol. 36, No. 2, February 2001.

S. B. Wicker, “ Error control Systems for Digital Communication and Storage ” , Prentice Hall, 1995.

R. K. Awalt. , “ Making the ASIC/FPGA Decision ” , Integrated System Design Magazine, July1999.

G. Ahlquist, B. Nelson, and M.Rice, “ Synthesis of Small and Fast Finite Field Multipliers for Field Programmable Gate Array ” , Proceeding of 5th one-year mliltary and Aerospace programmable logic device International Conference, Sept 2002.

Frederic Rivollon, “ Achieving Breakthrough Performance in Vertex-4 FPGA usher ” , May 2005.

Hanho Lee, “ A High Speed, Low capacity Reed Solomon decipherer for optical communicating ” , IEEE Transaction on circuits and System II, 2005.

B. Thomson, ” Turbo Product-Coding Hardware Makes Forward-Error Correction Possible with Significant Performance Advantages over Traditional Reed-Solomon and Viterbi Coding Approaches ” , Wireless Systems Design, June 2000

T. A. Mehta, “ Programmable Logic Devicess: Feasible Solutions for Implementing Error-Control Coding Functions ” , Integrated System Design Magazine.

E. J. Weldon, “ Mistake Correcting Codes and Trellis coded Modulation ” , University of Hawaii, 1996.

Essay Writing Service Features

Our Experience

No matter how complex your assignment is, we can find the right professional for your specific task. Contact Essay is an essay writing company that hires only the smartest minds to help you with your projects. Our expertise allows us to provide students with high-quality academic writing, editing & proofreading services.

Free Features

Free revision policy

$10Free bibliography & reference

$8Free title page

$8Free formatting

$8How Our Essay Writing Service Works

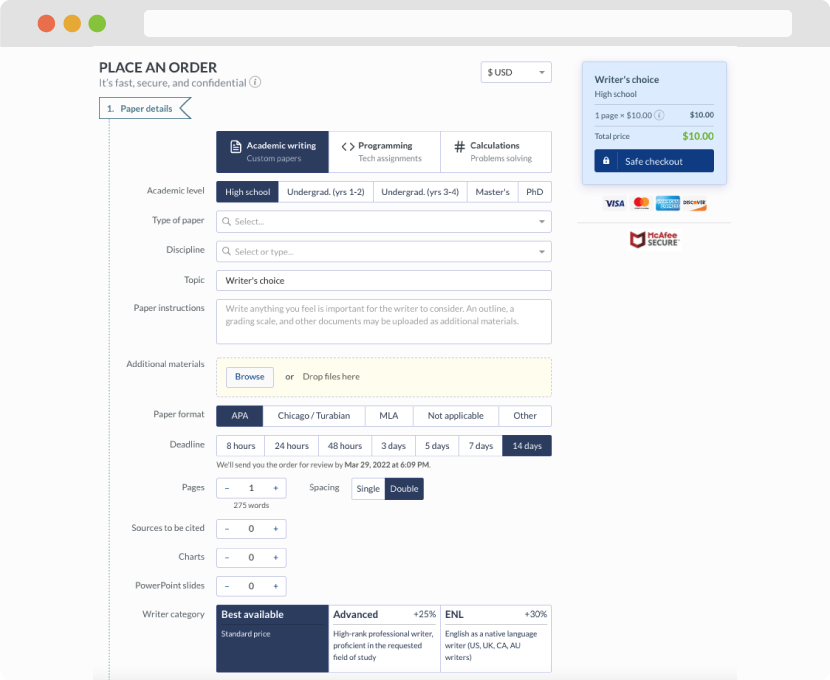

First, you will need to complete an order form. It's not difficult but, in case there is anything you find not to be clear, you may always call us so that we can guide you through it. On the order form, you will need to include some basic information concerning your order: subject, topic, number of pages, etc. We also encourage our clients to upload any relevant information or sources that will help.

Complete the order form

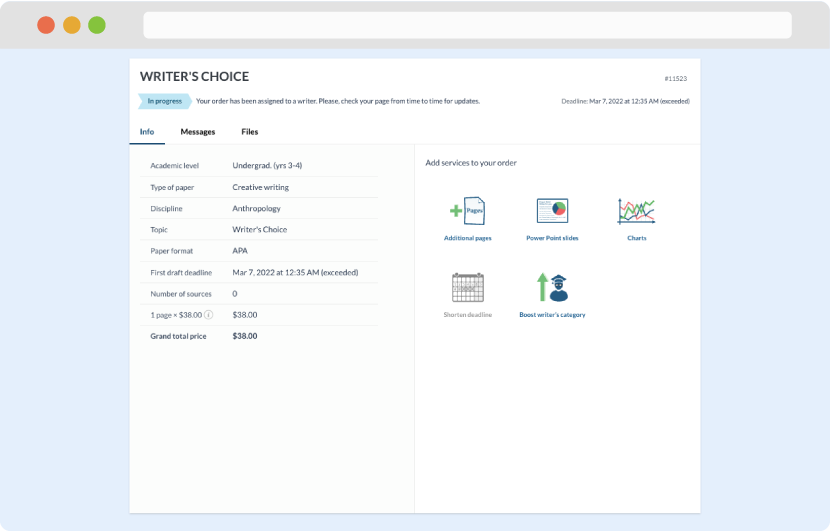

Once we have all the information and instructions that we need, we select the most suitable writer for your assignment. While everything seems to be clear, the writer, who has complete knowledge of the subject, may need clarification from you. It is at that point that you would receive a call or email from us.

Writer’s assignment

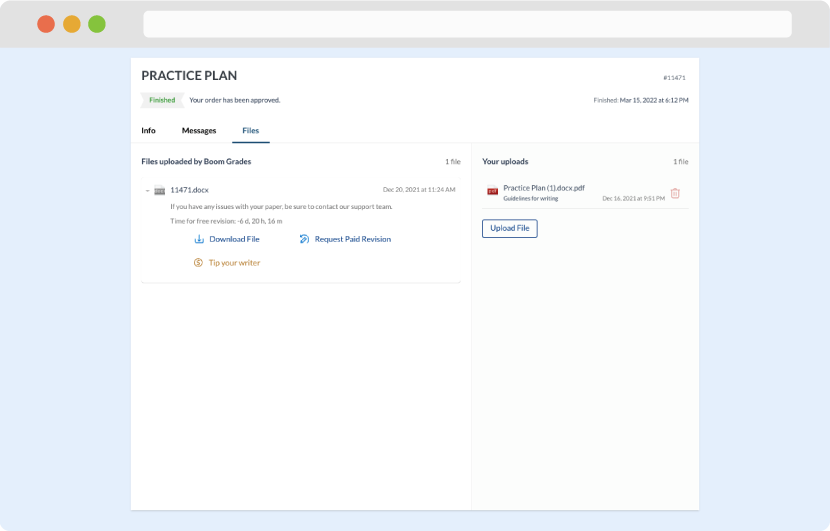

As soon as the writer has finished, it will be delivered both to the website and to your email address so that you will not miss it. If your deadline is close at hand, we will place a call to you to make sure that you receive the paper on time.

Completing the order and download