|

LS TTL |

ALS TTL |

CMOS |

HCMOS |

|

|

VIL |

– |

– |

– |

– |

|

VIH |

– |

– |

– |

– |

|

IIL |

-400µA |

– |

– |

-1 µA |

|

IIH |

40 µA |

– |

– |

1 µA |

|

VOL |

0.4 |

0.4 |

0.5 |

0.5 |

|

VOH |

2.7V |

6V |

8V |

-8V |

|

IOL |

4mA |

– |

1.4mA |

2.9mA |

|

LOH |

– |

– |

– |

– |

|

Fan-out |

20 |

20 |

2 |

10 |

|

Noise Margin |

– |

– |

– |

– |

The logic gates output is set with the feeds which could easily be connected. There are certain complex forms of the circuits, where there are no logic gate inputs that can be set for more than one particular output. The implementation is based on allowing the gate inputs to be properly wired without any additional interfacing circuitry process. The maximized fan-out is the output which is set through the capability of load driving where the gate inputs are set with the output that could be safely connected. The maximum limits for the fan-out is set with the logic family that is set for the datasheets. (Krishnamurthy, 2016). The complex analysis is based on the fan-in and the fan-out that is important for the interconnection of the logic families. The fan-out is determined through the source and the sinking currents of the output. The maximum source is set to supply or sink at the output where the current is needed depending upon the outputs of the high logic and the lower level of voltage. The specifications are based on the standards where the output could easily drive more inputs than the specifications by the fan-out. The logic gate could be set at the infinite input impedance with the zero output which allows the gate output for driving the number of the inputs in the gate. The connections are for handling the current with the gate inputs set for the flow below the level of the logic that cause error.

The noise margin is set with the amount where the signal tends to exceed the minimized operation amount. The communication is for the noise margin that is set in ratio by the signals with the minimized acceptable amount. The digital circuit works on the noise margin where the amount of the signal exceeds with the threshold for a proper 0 and 1 value. The noise margin is set for the CMOS chips that are more than that for the TTL. Here, the value is more for the power supply voltage that has been to make sure for the positive values with proper orientation. (Linn, 2016). The negative margin is set for the compromised operations where there is an outright failure as well.

The Karnaugh map helps in simplifying the expressions where there is a need for the calculations to work on the pattern recognition capability. It is based on the identification and the simulation with potential race conditions. The results are then from the truth table that is set for the two-dimensional grid system. The cell values are for representing the codes with the output value that will optimize the groups of the 1s and the 0s that are identified. The minimal Boolean expression represents the required logic where the real-world examinations are through the minimized number of the logic gates. The setup is based on the conditional statements which once minimized can lead to the development of the sum-of-products and the products-of-sums expression with the AND and OR operator. (Challa et al.., 2016). For the row and column, there are orders related to the Gray code where there is a need to handle the variable changes based on binary digits that are able to represent the function output mainly with the combination process. The construction of the canonical form where the information is set to simplify the expressions with the encircling the groups of 1s in the map. The minterms are for the final expressions for the group of 1s. The construction is based on the adjacent 1s that has been linked with the rectangular and the square boxed with the grouping based on the same state forms. It also allows the easy minimization of the functions as well as the combination of the inputs that is for the designer and to include the situations set in the rectangular group parts. For this, the major dedication is to eliminate the race conditions and work on the use of Karnaugh mapping where there is a race that exists mainly in between the different pairs of the adjacent setup. The nature for the same is gray coding, where there are glitches that depends mainly on the implementation physical nature. In the clocked logic, there have been desires to handle the value of time to meet the timing standards. The redundancy is in the form of the logical system approach where there is assurance of the race free performance to add and work on the elimination process with potential race hazard. The application of the De Morgan laws helps in creating a better potential with the horizontal and the vertical blocks that are interconnected. The block could easily be continued from the bottom, top, left or right with the wrap set for the minimization of the variable. (Laxman et al., 2016). The visualization process is for the k-map that can be considered to be cylindrical in the form, where the fields are at the edges with k-maps for the 4 different variables.

Boolean Expression:

Karnaugh Map:

|

ABCD |

00 |

01 |

11 |

10 |

|

00 |

||||

|

01 |

||||

|

11 |

||||

|

10 |

1 |

1 |

1 |

Thus, the expression is:

Circuit Diagram (Photographic Evidence):

Simulation has been attached in the Multisim file attached separately.

Truth Table:

|

A |

B |

C |

D |

F |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

The counter circuit has been set with the different number of the flip flops which have been connected in a separate form with the integrated circuits. There have been standards set for the d-type flip flops that is set to feed from the inverted output. The circuit can easily be able to store a particular bit which is then counted from zero to one before it starts to overflow. The counter works on incrementing for the clock cycle where the alternated are set in the transition of 0 to 1. The 4 bit has been set for the different operations which could be easily triggered by the repetition of the pulses called under the clock signals where the devices are using the synchronous circuits. The parameters are based on the consumption of power with the lower electromagnetic interference with modularity set in the large systems. The digital logical designs are based on the fact that there is no clock or the state set for the circuits where the changes are done with the input changes. The wait is mainly for the clock pulse with beginning the processing of the inputs and then working on the speeds and the circuits. The race condition works on the transitions where the inputs arrive and handle the systems which is built mainly for the better speed. (Wang et al., 2016). The logic required for this designing holds the digital system, where the functions are mainly without any clock signal and so there are certain logical elements which could not be relied on it. The quasi delay insensitivity with the incorporation of the multi-threshold CMOS helps in the different benefits through the use of timing constraints for a better performance and a lower area as well as power.

Flow Diagram

Sequence Table

|

Present State

|

Next State

|

|||||||||||||||

|

|

JA and KA

|

Q1Q2 |

|||||

|

Q3Q4 |

00 |

01 |

11 |

10 |

|

|

00 |

0 |

0 |

X |

X |

|

|

01 |

0 |

0 |

X |

X |

|

|

11 |

0 |

0 |

X |

X |

|

|

10 |

0 |

1 |

X |

X |

JA=Q2Q3

|

Q1Q2 |

|||||

|

Q3Q4 |

00 |

01 |

11 |

10 |

|

|

00 |

X |

X |

0 |

0 |

|

|

01 |

X |

X |

0 |

0 |

|

|

11 |

X |

X |

0 |

0 |

|

|

10 |

X |

X |

1 |

0 |

KA=Q2Q3

Multisim file attached separately.

The Multisim is the scheme where one need to set along with the NI Ultiboard where the creation is the simulation program with the circuit design set. The simulation based software also includes the microcontroller simulation with the integration import and the export feature that has been set for the circuit education. The applications are for the modular designing with the sub circuits, hierarchical blocks or the multi-page designing to create a custom of the title blocks with designing variants. The creation of the customer component is set with advanced schematic approach where the lesson also includes the features for the professional looking and the correct documentation process. The projects and the sharing of the design is through the use of blocks and buses. The simulation and the circuit designing gives an advancement to the analysis with optimizing the performance and reducing the errors in the design. The shortening of the time of the prototype includes the printed circuit board iterations and significant savings of cost. (Thiruvenkatachari et al., 2016). The analysis is based on the powerful technology with the ability to properly analyze the analog, digital and the power electronics that have been set for the all-new parameter forms, where the integration is based on the embedded targets. The forms are for the Standard Service Program where the self-placing online training is set with the modes that allow simulation in effective manner. The pattern is based on the architectural forms where the capturing of environment is through the virtual connections where the designs are set to meet and improve the net connections. It also includes the avoidance of all the unnecessary errors which is made for the circuit files with more stability process, and avoiding the errors with all the improper wiring or the connections. The communication is complete schematic for the decisions to make easy.

References

Krishnamurthy, S. (2016). U.S. Patent No. 9,503,950. Washington, DC: U.S. Patent and Trademark Office.

Linn, J. B. (2016). Using Multisim/Electronic Workbench In Basic Electricity Courses In Lieu Of Or To Complement Live Lab Experiments. Technology Interface International Journal, 57.

Challa, N., Mani, D., Rayapati, H. K., Surapaneni, R., Sanka, S., Krishnamoorthy, S., … & Babbadi, V. A. N. (2016). U.S. Patent No. 9,294,141. Washington, DC: U.S. Patent and Trademark Office.

Laxman, O. O., & Joshi, G. (2016). Bldc Motor Speed Control Using Co-Simulation Of Multisim and LABVIEW. International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering (IJIREEICE), 4(2), 35-39.

Thiruvenkatachari, B. S., Gupta, A. K., & Madhurantakam, S. R. (2016). U.S. Patent Application No. 15/052,412.

Wang, Z., Lei, T., Xi, X., & Sun, W. (2016). Fractional control and generalized synchronization for a nonlinear electromechanical chaotic system and its circuit simulation with Multisim. Turkish Journal of Electrical Engineering & Computer Sciences, 24(3), 1502-1515.

Essay Writing Service Features

Our Experience

No matter how complex your assignment is, we can find the right professional for your specific task. Contact Essay is an essay writing company that hires only the smartest minds to help you with your projects. Our expertise allows us to provide students with high-quality academic writing, editing & proofreading services.

Free Features

Free revision policy

$10Free bibliography & reference

$8Free title page

$8Free formatting

$8How Our Essay Writing Service Works

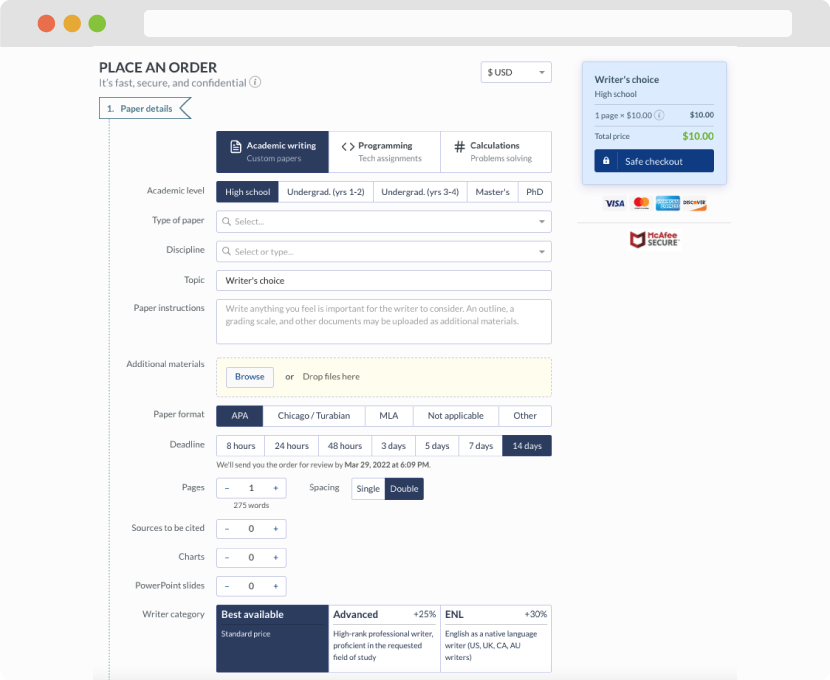

First, you will need to complete an order form. It's not difficult but, in case there is anything you find not to be clear, you may always call us so that we can guide you through it. On the order form, you will need to include some basic information concerning your order: subject, topic, number of pages, etc. We also encourage our clients to upload any relevant information or sources that will help.

Complete the order form

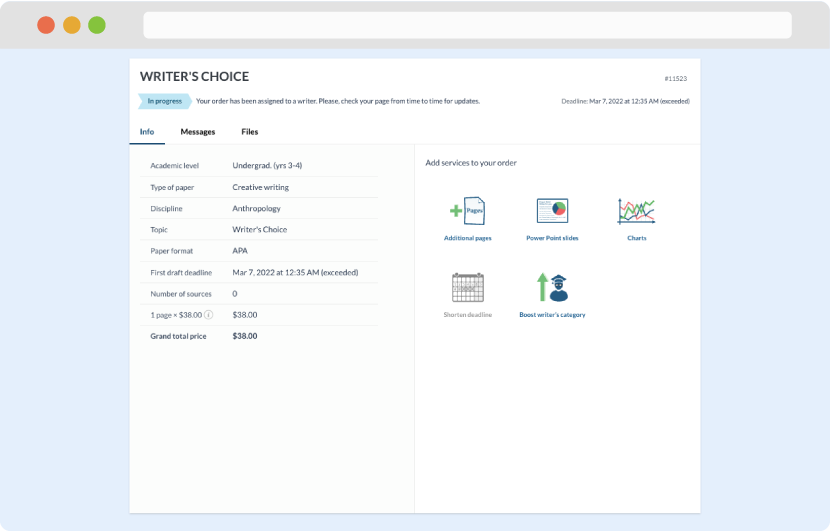

Once we have all the information and instructions that we need, we select the most suitable writer for your assignment. While everything seems to be clear, the writer, who has complete knowledge of the subject, may need clarification from you. It is at that point that you would receive a call or email from us.

Writer’s assignment

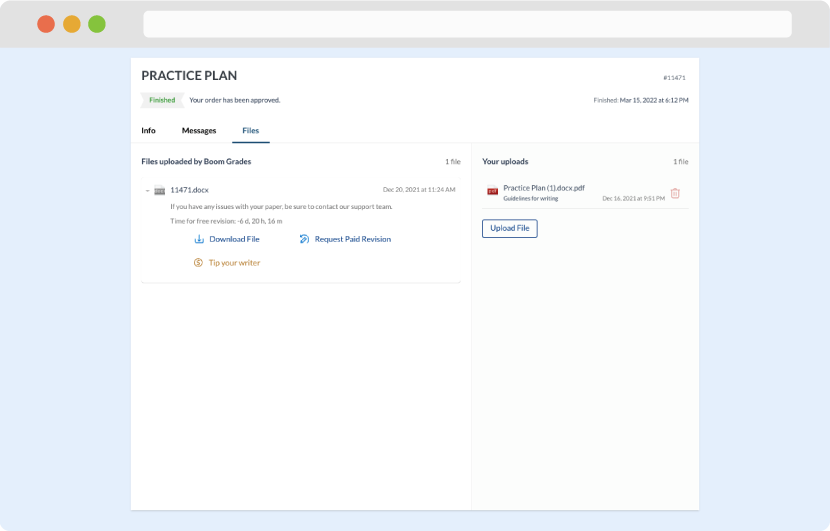

As soon as the writer has finished, it will be delivered both to the website and to your email address so that you will not miss it. If your deadline is close at hand, we will place a call to you to make sure that you receive the paper on time.

Completing the order and download