The processor ( CPU, for Central Processing Unit ) is the computing machine ‘s encephalon. It allows the processing of numeral informations, intending information entered in binary signifier, and the executing of instructions stored in memory. The first microprocessor ( Intel 4004 ) was invented in 1971. It was a 4-bit computation device with a velocity of 108 kilohertz. Since so, microprocessor power has grown exponentially.

The processor ( called CPU, for Central Processing Unit ) is an electronic circuit that operates at the velocity of an internal clock thanks to a quartz crystal that, when subjected to an electrical currant, send pulsations, called “ extremums ” .

The clock velocity ( besides called rhythm ) , corresponds to the figure of pulsations per second, written in Hertz ( Hz ) . Therefore, a 200 MHz computing machine has a clock that sends 200,000,000 pulsations per second.

With each clock extremum, the processor performs an action that corresponds to an direction or a portion there of. A step called CPI ( Cycles Per Instruction ) gives a representation of the mean figure of clock rhythms required for a microprocessor to put to death an direction.

A microprocessor power can therefore be characterized by the figure of instructions per second that it is capable of treating. MIPS ( 1000000s of instructions per second ) is the unit used and corresponds to the processor frequence divided by the CPI.

One of the primary ends of computing machine designers is to plan computing machines that are more cost effectual than their predecessors. Cost-effectiveness includes the cost of hardware to fabricate the machine, the cost of scheduling, and costs incurred related to the architecture in debugging.

Both the initial hardware and subsequent plans. If we review the history of computing machine households we find that the most common architectural alteration is the tendency toward of all time more complex machines. Presumably this extra complexness has a positive trade off with respect to the cost effectivity of newer theoretical accounts.

The engine of the computing machine revolution is the microprocessor. It has led to new innovations, such as FAX machines and personal computing machines, every bit good as adding intelligence to bing devices, such as wrist watchs and cars. Furthermore, its public presentation has improved by a factor of approximately 10,000 in the 25 old ages since its birth in 1971.

This addition coincided with the debut of Reduced Instruction Set Computers ( RISC ) . The direction set is the hardware “ linguistic communication ” in which the package tells the processor what to make. Surprisingly, cut downing the size of the direction set — extinguishing certain instructions based upon a careful quantitative analysis, and necessitating these seldom-used instructions to be emulated in package — can take to higher public presentation, for several grounds: –

.from the 701 to the 709 [ Cocke80 ] . The 701 CPU was approximately 10 times every bit fast as the nucleus chief memory this made any primitives that were implemented as subprograms much slower than primitives that were instructions. 709 more cost-efficient than the 701. Since so, many “ higher-level ” instructions have been added to machines in an effort to better public presentation.

Microprogrammed control allows the execution of complex architectures more cost-effectively than hardwired control.Advances in incorporate circuit memories made in the late 60 ‘s and early 70 ‘s have caused microprogrammed control to be the more cost-efficient attack in about every instance. Once the determination is made to utilize microprogrammed control, the cost to spread out an direction set is really little ; merely a few more words of control shop.

Examples of such instructions are threading redacting, integer-to-floating transition, and mathematical operations such as multinomial rating.

With early computing machines, memory was really expensive. It was hence cost effectual to hold really compact plans.

Trying to obtain code denseness by increasing the complexness of the direction set is frequently a double-edged the cost of 10 % more memory is frequently far cheaper than the cost of squashing 10 % out of the CPU by architectural “ inventions ” .

Unfortunately, the primary end of a computing machine company is non to plan the most cost-efficient computing machine ; the primary end of a computing machine company is to do the most money by selling computing machines. In order to sell computing machines makers must convert clients that their design is superior to their competitor’s.In order to maintain their occupations, designers must maintain selling new and better designs to their internal direction.

Coincident with selling scheme is the sensed demand for upward compatibility. Upward compatibility means that the primary manner to better a design is to add new, and normally more complex, characteristics. Seldom are instructions or turn toing manners removed from an architecture, ensuing in a gradual addition in both the figure and complexness of instructions over a series of computing machines.

As the usage of high degree linguistic communications becomes progressively popular, makers have become eager to supply more powerful instructions to back up them. Unfortunately there is small grounds to propose that any of the more complicated direction sets have really provided such support.The attempt to back up high-ranking linguistic communications is commendable, but we feel that frequently the focal point has been on the incorrect issues.

The rise of timesharing required that computing machines be able to react to disrupt with the ability to hold an put to deathing procedure and re-start it at a ulterior clip. Memory direction and paging to boot required that instructions could be halted before completion and subsequently restarted.

The acronym RISC ( pronounced hazard ) , for decreased direction set computer science, represents a CPU design scheme stressing the penetration that simplified instructions that “ make less ” may still supply for higher public presentation if this simpleness can be utilized to do instructions put to death really rapidly. Many proposals for a “ precise ” definition have been attempted, and the term is being easy replaced by the more descriptive load-store architecture.

Bing an old thought, some facets attributed to the first RISC-labeled designs ( around 1975 ) include the observations that the memory restricted compilers of the clip were frequently unable to take advantage of characteristics intended to ease cryptography, and that complex turn toing inherently takes many rhythms to execute. It was argued that such maps would better be performed by sequences of simpler instructions, if this could give executions simple plenty to get by with truly high frequences, and little plenty to go forth room for many registries, factoring out slow memory entrees. Uniform, fixed length an direction with arithmetic ‘s restricted to registries was chosen to ease direction pipelining in these simple designs, with particular load-store instructions accessing memory.

The basic RISC rule: “ A simpler CPU is a faster CPU ” .

The focal point of the RISC design is decrease of the figure and complexness of instructions in the ISA.

For any given degree of general public presentation, a RISC bit will typically hold far fewer transistors dedicated to the nucleus logic which originally allowed interior decorators to increase the size of the registry set and increase internal correspondence.

Other characteristics, which are typically found in RISC architectures, are:

Fixed length instructions which

A complex direction set computing machine ( CISC, pronounced like “ sisk ” ) is a computing machine direction set architecture ( ISA ) in which each direction can put to death several low-level operations, such as a burden from memory, an arithmetic operation, and a memory shop, all in a individual direction.

Some instructions were added that were ne’er intended to be used in assembly linguistic communication but fit well with compiled high degree linguistic communications. Compilers were updated to take advantage of these instructions. The benefits of semantically rich instructions with compact encryptions can be seen in modern processors every bit good, peculiarly in the high public presentation section where caches are a cardinal constituent ( as opposed to most embedded systems ) . This is because these fast, but complex and expensive, memories are inherently limited in size, doing compact code beneficial. Of class, the cardinal ground they are needed is that chief memories ( i.e. dynamic RAM today ) remain slow compared to a ( high public presentation ) CPU-core.

This tabular array is taken from an IEEE tutorial on RISC architecture.

| CISC Type Computers | RISC Type | ||||

| IBM 370/168 | VAX-11/780 | Intel 8086 | RISC I | IBM 801 | |

| Developed | 1973 | 1978 | 1978 | 1981 | 1980 |

| Instruction manuals | 208 | 303 | 133 | 31 | 120 |

| Direction size ( spots ) | 16 – 48 | 16 – 456 | 8 – 32 | 32 | 32 |

| Addressing Manners | 4 | 22 | 6 | 3 | 3 |

| General Registers | 16 | 16 | 4 | 138 | 32 |

| Control Memory Size | 420 Kb | 480 Kb | Not given | 0 | 0 |

| Cache Size | 64 Kb | 64 Kb | Not given | 0 | Not given |

However, presents, the difference between RISC and CISC french friess is acquiring smaller and smaller. RISC and CISC architectures are going more and more likewise. Many of today ‘s RISC french friess support merely as many instructions as yesterday ‘s CISC french friess. The PowerPC 601, for illustration, supports more instructions than the Pentium. Yet the 601 is considered a RISC bit, while the Pentium is decidedly CISC.

Today ‘s microprocessors are approximately 10,000 times faster than their ascendants. And microprocessor-based computing machine systems now cost merely 1/40th every bit much as their ascendants, when rising prices is considered. The consequence: an overall cost-performance betterment of approximately 1,000,000, in merely 25 old ages! This extraordinary progress is why calculating dramas such a big function in today ‘s universe. Had the research at universities and industrial research labs non occurred — had the complex interplay between authorities, industry, and academia non been so successful — a comparable progress would still be old ages off.

Microprocessor public presentation can go on to duplicate every 18 months beyond the bend of the century. This rate can be sustained by continued research invention. Significant new thoughts will be needed in the following decennary to go on the gait ; such thoughts are being developed by research groups today.

The research that led to the development of RISC architectures represented an of import displacement in computing machine scientific discipline, with accent traveling from hardware to package. The eventual laterality of RISC engineering in high-performance workstations from the mid to late 1980s was a merited success.

In recent old ages CISC processors have been designed that successfully get the better of the restrictions of their direction set architecture that is more elegant and power-efficient, but compilers need to be improved and clock velocities need to increase to fit the aggressive design of the latest Intel processors.

Essay Writing Service Features

Our Experience

No matter how complex your assignment is, we can find the right professional for your specific task. Contact Essay is an essay writing company that hires only the smartest minds to help you with your projects. Our expertise allows us to provide students with high-quality academic writing, editing & proofreading services.

Free Features

Free revision policy

$10Free bibliography & reference

$8Free title page

$8Free formatting

$8How Our Essay Writing Service Works

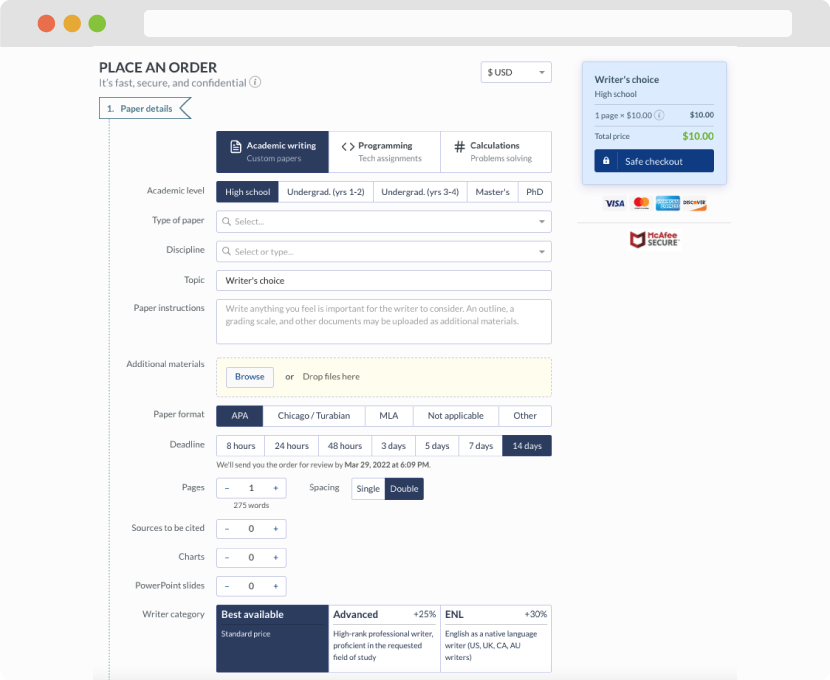

First, you will need to complete an order form. It's not difficult but, in case there is anything you find not to be clear, you may always call us so that we can guide you through it. On the order form, you will need to include some basic information concerning your order: subject, topic, number of pages, etc. We also encourage our clients to upload any relevant information or sources that will help.

Complete the order form

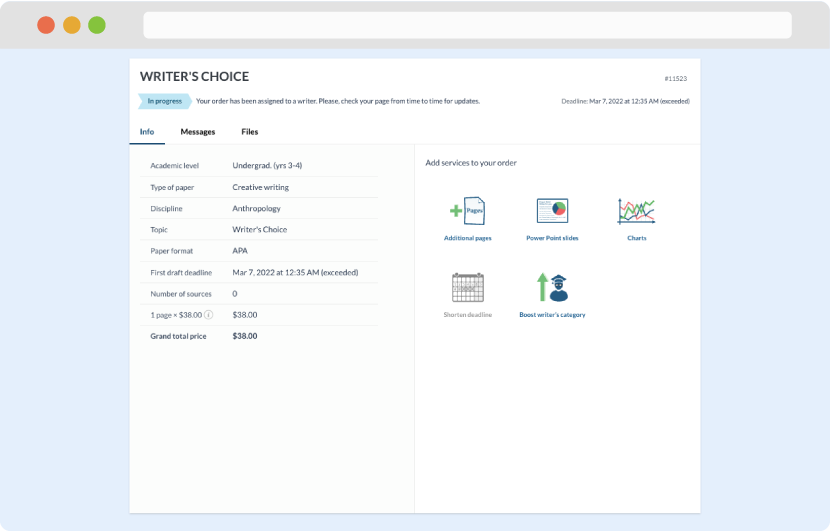

Once we have all the information and instructions that we need, we select the most suitable writer for your assignment. While everything seems to be clear, the writer, who has complete knowledge of the subject, may need clarification from you. It is at that point that you would receive a call or email from us.

Writer’s assignment

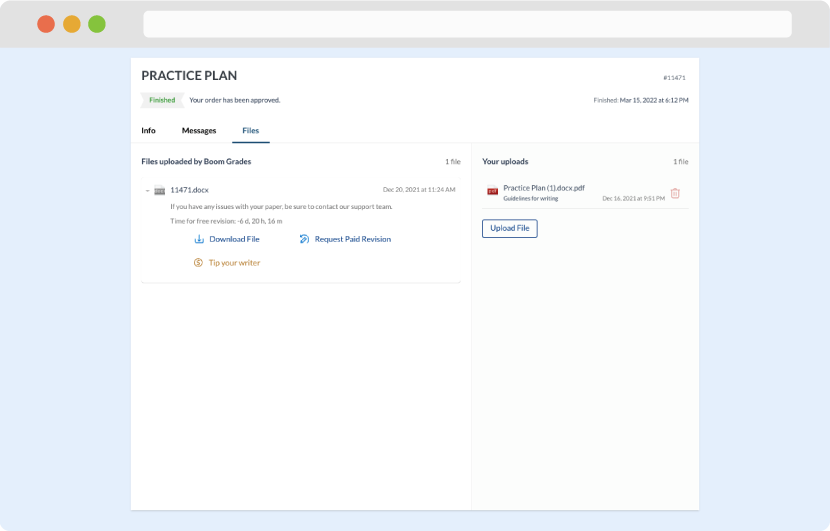

As soon as the writer has finished, it will be delivered both to the website and to your email address so that you will not miss it. If your deadline is close at hand, we will place a call to you to make sure that you receive the paper on time.

Completing the order and download